# PATENT 12480-000032/US

# IN THE U.S. PATENT AND TRADEMARK OFFICE

Applicant(s):

Koichi MIYACHI et al.

Conf. No.:

7380

Application No:

10/742,933

Group:

2173

Filed:

December 23, 2003

Examiner:

Unknown

For:

A METHOD AND DEVICE FOR DRIVING DISPLAY DEVICE, AND

PROGRAM AND RECORDING MEDIUM THEREFOR

# **PRIORITY LETTER**

Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450 June 2, 2004

Dear Sirs:

Pursuant to the provisions of 35 U.S.C. 119, enclosed is a certified copy of the following priority document:

Application No.

**Date Filed**

Country

2002-381618

December 27, 2002

**JAPAN**

In support of Applicants' priority claim, please enter this document into the file.

Respectfully submitted,

HARNESS, DICKEY & PIERCE, P.L.C.

By

Donald J. Daley, Reg/No. 34,313

P.O. Box 8910

Reston, Virginia 20195

(703) 668-8000

DJD/bof

# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出 願 年 月 日 Date of Application:

2002年12月27日

出 願 番 号 Application Number:

特願2002-381618

[ST. 10/C]:

Applicant(s):

[JP2002-381618]

出 願 人

シャープ株式会社

特許庁長官 Commissioner, Japan Patent Office 2003年12月19日

【書類名】 特許願

【整理番号】 02J04363

【提出日】 平成14年12月27日

【あて先】 特許庁長官 殿

【国際特許分類】 G09G 3/20 621

G09G 3/36

G09F 9/35 305

【発明者】

【住所又は居所】 大阪府大阪市阿倍野区長池町22番22号 シャープ株

式会社内

【氏名】 宮地 弘一

【発明者】

【住所又は居所】 大阪府大阪市阿倍野区長池町22番22号 シャープ株

式会社内

【氏名】 宮田 英利

【発明者】

【住所又は居所】 大阪府大阪市阿倍野区長池町22番22号 シャープ株

式会社内

【氏名】 陣田 章仁

【発明者】

【住所又は居所】 大阪府大阪市阿倍野区長池町22番22号 シャープ株

式会社内

【氏名】 富沢 一成

【発明者】

【住所又は居所】 大阪府大阪市阿倍野区長池町22番22号 シャープ株

式会社内

【氏名】 塩見 誠

【特許出願人】

【識別番号】

000005049

【氏名又は名称】 シャープ株式会社

【代理人】

【識別番号】

100080034

【弁理士】

【氏名又は名称】

原 謙三

【電話番号】

06-6351-4384

【選任した代理人】

【識別番号】

100113701

【弁理士】

【氏名又は名称】 木島 隆一

【選任した代理人】

【識別番号】

100116241

【弁理士】

【氏名又は名称】 金子 一郎

【手数料の表示】

【予納台帳番号】

003229

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 0208489

【プルーフの要否】

要

# 【書類名】 明細書

【発明の名称】 表示装置の駆動方法、表示装置の駆動装置、および、そのプログラム

### 【特許請求の範囲】

### 【請求項1】

複数フィールドの映像信号から1フレームの映像が構成されるインタレース信 号に基づいて、各フレームの映像を表示する画素群を駆動する駆動方法であり、

現フィールドの映像信号に基づいて、1フレーム分の映像を表示する画素群を 駆動するための駆動信号を生成する駆動信号生成工程と、

前フィールドの映像信号を参照して、上記画素群の駆動信号を変調する変調工程とを含んでいる表示装置の駆動方法において、

上記変調工程の前に実施され、前フィールドの映像信号を補間して、1フレーム分の映像信号を生成する前フィールド補間工程と、

上記変調工程の前に実施され、現フィールドの映像信号を補間して、1フレーム分の映像信号を生成する現フィールド補間工程とを含み、

上記変調工程では、各画素の駆動信号を変調する際、前フィールドの映像信号のうち、当該画素への駆動信号を生成するための映像信号を参照して、当該画素の駆動信号を変調することを特徴とする表示装置の駆動方法。

# 【請求項2】

上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する行の映像信号と同一内容の映像信号によって補間することを特徴とする請求項1記載の表示装置の駆動方法。

#### 【請求項3】

上記1フレームは、2フィールドから構成されており、

上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する2つの行の映像信号を平均した映像信号によって補間することを特徴とする請求項1記載の表示装置の駆動方法。

# 【請求項4】

上記1フレームは、2フィールドから構成されており、

上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、補間する行に連続する行であって、しかも、補間対象のフィールドを構成する2つの行の映像信号に基づいて、補間する行の映像信号を生成すると共に、上記2つの行の一方を構成する複数の画素への映像信号と、他方を構成する複数の画素への映像信号とに基づいて、補間する行の1つの画素への映像信号を生成することを特徴とする請求項1記載の表示装置の駆動方法。

## 【請求項5】

上記1フレームは、2フィールドから構成されており、

上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像 信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィール ドを構成する2つの行の映像信号と、補間対象に隣接するフィールドの映像信号 とに基づいて補間することを特徴とする請求項1記載の表示装置の駆動方法。

# 【請求項6】

1フレームは、2フィールドから構成されており、

2フィールド前の映像信号と、現フィールドの映像信号との比較結果を参照して、上記変調工程における変調の程度を調整する調整工程を含んでいることを特徴とする請求項1記載の表示装置の駆動方法。

# 【請求項7】

上記調整工程では、2フィールド前の映像信号と現フィールドの映像信号とが 概ね同じであれば、上記変調工程における変調を阻止することを特徴とする請求 項6記載の表示装置の駆動方法。

### 【請求項8】

上記調整工程では、2フィールド前の映像信号と現フィールドの映像信号との差が予め定められた範囲であれば、両者の差に応じて、変調を抑制する程度を、変調を抑制しないレベルから、変調を阻止するレベルにまで徐々に変化させることを特徴とする請求項6記載の表示装置の駆動方法。

#### 【請求項9】

上記変調工程では、前フィールドから現フィールドへの階調遷移を強調するように、上記画素群の駆動信号が変調されており、

さらに、上記変調工程における階調遷移強調の程度は、第1の階調から第2の 階調への階調遷移を最も強調したときの応答速度と、第2の階調から第1の階調 への階調遷移を最も強調したときの応答速度とのうちの速い方を、遅い方に近づ けることによって、ある画素の前フィールドから現フィールドへの階調遷移が、 上記第1の階調から第2の階調への階調遷移と第2の階調から第1の階調への階 調遷移とを繰り返すときに、当該画素の時間的積分輝度が上記第1の階調から第 2の階調までの間の値になるように設定されていることを特徴とする請求項1記 載の表示装置の駆動方法。

# 【請求項10】

上記変調工程では、上記変調工程における階調遷移強調の程度が、各階調遷移のうち、最も強調しても一番遅い階調遷移の応答速度に、他の階調遷移の応答速度が略一致するように、他の階調遷移強調の程度が抑えて設定されていることを特徴とする請求項9記載の表示装置の駆動方法。

### 【請求項11】

複数フィールドの映像信号から1フレームの映像が構成されるインタレース信号に基づいて、現フィールドの映像信号と前フィールドの映像信号とを生成する 現および前フィールドの映像信号生成手段と、

1フレームの映像を表示する画素群を駆動するための駆動信号として、上記現フィールド映像信号に応じた駆動信号であって、上記前フィールド映像信号に応じて変調された駆動信号を生成する駆動信号生成手段とを有する表示装置の駆動装置において、

上記現および前フィールドの映像信号生成手段は、前フィールドを構成する各行の間を補間して、上記前フィールド映像信号として、1フレーム分の前フィールド映像信号を生成する前フィールド補間手段と、

現フィールドを構成する各行の間を補間して、上記現フィールド映像信号として、1フレーム分の現フィールド映像信号を生成する現フィールド補間手段とを 備え、 上記駆動信号生成手段は、上記各画素の駆動信号を生成する際、上記前フィールド映像信号のうち、当該画素への駆動信号を生成するための映像信号を参照して、当該画素の駆動信号を変調することを特徴とする表示装置の駆動装置。

### 【請求項12】

上記インタレース信号では、2フィールドの映像から1フレームの映像が構成されており、

上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行 分記憶し、1行分の映像信号を、上記インタレース信号のドットクロックの2倍 の周波数で2回出力するラインメモリを備え、

上記前フィールド補間手段は、現フィールドを構成する各行の映像信号を格納 し、次のフィールドまで記憶するフィールドメモリと、

上記ラインメモリの出力に基づいて、現フィールドを構成する各行の映像信号を上記フィールドメモリに格納すると共に、前のフィールドを構成する各行の映像信号を、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波数で2回出力させる制御手段とを備えていることを特徴とする請求項11記載の表示装置の駆動装置。

#### 【請求項13】

上記インタレース信号では、2フィールドの映像から1フレームの映像が構成 されており、

上記現および前フィールドの映像信号生成手段は、上記インタレース信号を1フィールド分遅らせて出力するフィールドメモリを備え、

上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行 分記憶すると共に、当該1行分の映像信号を、上記インタレース信号のドットク ロックの2倍の周波数で2回出力する現フィールドラインメモリを備え、

上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1 行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリ と同じ周波数で2回出力する前フィールドラインメモリを備えていることを特徴 とする請求項11記載の表示装置の駆動装置。

#### 【請求項14】

5/

現フィールドの映像信号を、現フィールドと映像信号の位置が同一の近接するフィールドまで記憶し、同一位置フィールド映像信号として出力する同一位置フィールド映像信号生成手段を備え、

上記駆動信号生成手段は、上記同一位置フィールド映像信号と現フィールド映像信号とを比較し、比較結果に応じて、前フィールドから現フィールドへの階調 遷移強調の程度を変更して、駆動信号を生成することを特徴とする請求項11記載の表示装置の駆動装置。

# 【請求項15】

上記インタレース信号では、2フィールドの映像から1フレームの映像が構成 されており、

上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行 分記憶し、1行分の映像信号を、上記インタレース信号のドットクロックの2倍 の周波数で2回出力する現フィールドラインメモリを備え、

さらに、現フィールドの映像信号を2つ後のフィールドまで記憶するフィールドメモリと、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波数で、前フィールドの1行分の映像信号と前々フィールドの1行分の映像信号と交互に出力させる制御手段と、上記フィールドメモリが出力する前々フィールドの映像信号を1行分記憶すると共に、上記前々フィールド映像信号として、上記現フィールドラインメモリと同じ周波数で当該1行分の映像信号を2回出力する前々フィールドラインメモリとが設けられ、

上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1 行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリ と同じ周波数で2回出力する前フィールドラインメモリを備え、

上記駆動信号生成手段は、上記現フィールド補間手段が出力する現フィールド映像信号と上記前々フィールド映像信号とを上記各画素毎に比較して、上記各画素毎に、比較結果を出力する比較手段と、比較結果に基づいて、各画素の駆動信号の変調の程度を調整する調整手段とを備えていることを特徴とする請求項11記載の表示装置の駆動装置。

### 【請求項16】

上記インタレース信号では、2フィールドの映像から1フレームの映像が構成 されており、

上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行 分記憶し、1行分の映像信号を、上記インタレース信号のドットクロックの2倍 の周波数で2回出力する現フィールドラインメモリを備え、

さらに、現フィールドの映像信号を2つ後のフィールドまで記憶するフィールドメモリと、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波数で、前フィールドの1行分の映像信号と前々フィールドの1行分の映像信号とを交互に出力させる制御手段とが設けられ、

上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1 行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリ と同じ周波数で2回出力する前フィールドラインメモリを備え、

上記駆動信号生成手段は、上記現フィールド補間手段が出力するフィールド映像信号を構成する各行の映像信号のうち、1行おきの映像信号と、上記前々フィールド映像信号とを上記各画素毎に比較して、上記各画素毎に、比較結果を出力する比較手段と、比較結果を1行分記憶すると共に、1行分の比較結果を、上記現フィールドラインメモリと同じ周波数で2回出力する比較結果ラインメモリと、当該比較結果ラインが出力する各画素の比較結果に応じて、当該画素の駆動信号の変調の程度を調整する調整手段とを備えていることを特徴とする請求項11記載の表示装置の駆動装置。

# 【請求項17】

請求項1記載の各工程をコンピュータに実行させるプログラム。

#### 【発明の詳細な説明】

[0001]

#### 【発明の属する技術分野】

本発明は、表示装置の駆動方法、表示装置の駆動装置、および、そのプログラムに関するものである。

[0002]

#### 【従来の技術】

比較的少ない電力で駆動可能な液晶表示装置は、携帯機器のみならず、据え置き型の機器の表示装置として、広く使用されている。当該液晶表示装置は、CRT (Cathode-Ray Tube)などと比較すると、応答速度が遅く、遷移階調によって、通常のフレーム周波数(60Hz)に対応した書き換え時間(16.7msec)で応答が完了しないこともあるため、前回から今回への階調遷移を強調するように、駆動信号を変調して駆動する方法も採用されている(後述の特許文献1参照)。

## [0003]

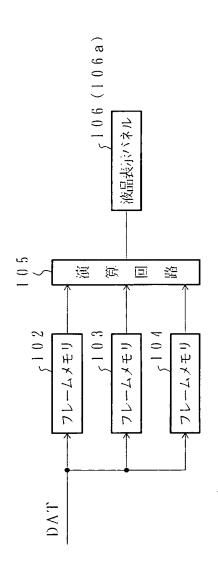

具体的には、図19に示すように、表示装置101へ入力された現フレームの映像データは、フレームメモリ102~104のいずれかに入力され、次のフレームまで記憶される。一方、演算回路105は、フレームメモリ102~105から、現フレームの映像信号のデータと、前フレームの映像信号のデータとを読み出し、前フレームから現フレームへの階調遷移を強調するように補正する。さらに、演算回路105から出力された補正映像信号は、液晶表示パネル106へ入力され、液晶表示パネル106は、当該補正映像信号に基づいて、各画素を駆動する。

### [0004]

例えば、前フレームFR(k-1) から現フレームFR(k) への階調遷移がライズ駆動の場合、前回から今回への階調遷移を強調するように、具体的には、現フレームFR(k) の映像データD(i, j, k) が示す電圧レベルよりも高いレベルの電圧を画素へ印加する。

#### [0005]

この結果、階調が遷移するとき、現フレームFR(k)の映像データD(i,j,k)が示す電圧レベルを最初から印加する場合の輝度レベルと比較して、画素の輝度レベルは、より急峻に増大し、より短い期間で、上記現フレームFR(k)の映像データD(i,j,k)に応じた輝度レベル近傍に到達する。これにより、液晶の応答速度が遅い場合であっても、液晶表示パネルの応答速度を向上できる。

# [0006]

一方、上記液晶表示パネルは、上記CRTとは異なり、自ら発光せず、バック

ライトなどの光源から入射される光の出射光量を変更して、各画素の輝度を設定 しているため、暗表示時にも、光源は電力を消費している。

### [0007]

したがって、このような液晶表示パネルでは、インタレース信号に基づいて、 各画素を駆動する際、現フィールドの映像信号に基づいて、全画素を駆動する駆動方法が採用されることが多い。

## [0008]

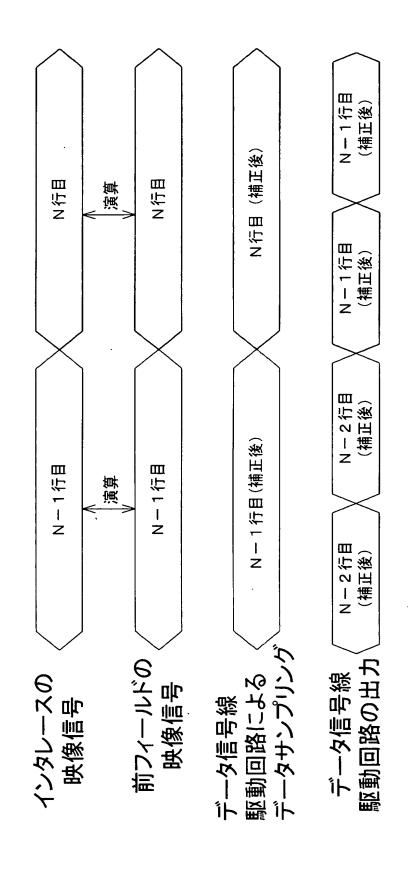

具体的には、図20に示すように、液晶表示パネルにインタレース信号が入力 された場合、液晶表示パネルのデータ信号線駆動回路は、現フィールドを構成す る各水平ラインの映像データをサンプリングする。

### [0009]

一方、上記データ信号線駆動回路は、インタレース信号が入力された場合、1 水平ライン分のサンプリング結果によって、2水平ライン分の画素を駆動している。これにより、2水平ラインに同じデータが書き込まれ、液晶表示パネルは、インタレース信号が入力されているにも拘わらず、現フィールドの映像信号に基づいて、全画素を駆動できる。この結果、現フィールドに対応する画素以外の画素を暗表示する構成よりも、表示装置の輝度を向上できる。

#### [0010]

## 【特許文献1】

特開2002-116743号公報(公開日:2002年4月19日)

#### [0011]

#### 【発明が解決しようとする課題】

しかしながら、図19記載の液晶表示パネルとして、図20に示すタイミングで動作する液晶表示パネルを使用し、演算回路が前フィールドから現フィールドへの階調遷移を強調して、補正映像信号を生成すると、階調遷移強調時の参照元の不一致に起因する誤変調が発生し、表示装置の表示品質を低下させる虞れがある。

# [0012]

具体的には、当該構成では、図21に示すように、インタレース信号が入力さ

れると、図19に示す演算回路105は、前フィールドのN行目の水平ラインと、現フィールドのN行目の水平ラインとを演算して、前フィールドから現フィールドへの階調遷移を強調するように補正した補正映像信号を生成する。一方、図19に示す液晶表示パネル106aのデータ信号線駆動回路は、図20と同様に、補正映像信号をサンプリングして、1水平ライン分のサンプリング結果を2回出力する。

# [0013]

ところが、現フィールドを構成する各行の位置は、前フィールドを構成する各行の位置と異なっており、図22に示すように、奇数フィールドにおいて、N行目(例えば、2行目)の水平ラインは、フレームの2N-1行目(3行目)になり、偶数フィールドにおいて、N行目の水平ラインは、フレームの2N行目(4行目)になる。

### $[0\ 0\ 1\ 4\ ]$

したがって、上述したように、液晶表示パネル106aのデータ信号線駆動回路が、1水平ライン分の映像信号を2回出力すると、図23に示すように、奇数フィールドでは、フレームの1行目の水平ラインと2行目の水平ラインとが同じデータになり、偶数フィールドでは、2行目の水平ラインと3行目の水平ラインとが同じデータになる。

#### $[0\ 0\ 1\ 5]$

ところが、図22に示すように、演算回路105は、前フィールドのN行目の 水平ラインと、現フィールドのN行目の水平ラインとを演算して、現フィールド のN行目の水平ライン分の補正映像信号を生成している。

# [0016]

したがって、図24に示すように、例えば、フレームの2行目の画素を駆動する補正映像信号は、奇数および偶数フィールドの双方において、現および前フィールドの1行目のデータ同士を演算して生成されるのに対して、フレームの3行目の画素は、奇数フィールドでは、2行目のデータ同士の演算により生成した補正映像信号によって駆動されているにも拘わらず、偶数フィールドでは、1行目のデータ同士の演算により生成した補正映像信号によって駆動される。なお、図

24では、同じ内容のデータを太線で囲って示している。

# [0017]

この結果、演算回路105は、2行目では、正しい映像信号を参照して、正しく階調遷移を強調できるが、3行目では、正しい映像信号を参照できないため、正しく階調遷移を強調できない。この結果、画素の階調遷移を誤って強調してしまい、本来の表示すべき階調とは異なる階調を表示する虞れがある。

# [0018]

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、各フィールド毎に、1フレーム分の画素群を駆動することによって、輝度を増大すると共に、前フィールドの映像信号を参照して駆動信号を変調することによって、画素の応答速度を向上できるにも拘わらず、演算対象のズレに起因する誤変調の発生を防止し、表示品質の良い表示装置を実現することにある。

### [0019]

# 【課題を解決するための手段】

本発明に係る表示装置の駆動方法は、上記課題を解決するために、複数フィールドの映像信号から1フレームの映像が構成されるインタレース信号に基づいて、各フレームの映像を表示する画素群を駆動する駆動方法であり、現フィールドの映像信号に基づいて、1フレーム分の映像を表示する画素群を駆動するための駆動信号を生成する駆動信号生成工程と、前フィールドの映像信号を参照して、上記画素群の駆動信号を変調する変調工程とを含んでいる表示装置の駆動方法において、以下の手段を講じたことを特徴としている。

# [0020]

すなわち、上記変調工程の前に実施され、前フィールドの映像信号を補間して、1フレーム分の映像信号を生成する前フィールド補間工程と、上記変調工程の前に実施され、現フィールドの映像信号を補間して、1フレーム分の映像信号を生成する現フィールド補間工程とを含み、上記変調工程では、各画素の駆動信号を変調する際、前フィールドの映像信号のうち、当該画素への駆動信号を生成するための映像信号を参照して、当該画素の駆動信号を変調する。

# [0021]

上記構成では、前フィールドの映像信号を参照しているものの、基本的には、現フィールドの映像信号に基づいて、1フレーム分の映像を表示する画素群が駆動される。したがって、他のフィールドの映像信号に対応する画素が消灯している場合と比較して、表示装置の輝度を増大できる。また、前フィールドの映像信号を参照して、現フィールドの駆動信号を変調しているので、現フィールドの映像信号のみに基づいて画素群を駆動する場合に比べて、画素の応答速度を向上できる。

# [0022]

さらに、上記構成では、変調工程の前に、前フィールドの映像信号および前フィールドの映像信号を補間して、それぞれ1フレーム分の映像信号が生成されており、変調工程では、前フィールドの映像信号のうち、当該画素への駆動信号を 生成するための映像信号を参照して、当該画素の駆動信号を変調する。

### [0023]

したがって、各フィールド毎に、1フレーム分の画素群が駆動されることによって、輝度を増大し、前フィールドの映像信号を参照して駆動信号を変調することによって、画素の応答速度を向上できるにも拘わらず、比較対象のズレに起因する誤変調が発生しない。この結果、表示品質の良い表示装置を実現できる。

#### [0024]

さらに、上記構成では、前フィールドの映像信号を参照して変調しているので、変調によって画素の応答速度を向上できるにも拘わらず、前フレームの映像信号を参照して変調する場合よりも、変調に必要な記憶容量を削減できる。

#### $[0\ 0\ 2\ 5]$

また、回路構成の簡略化が特に求められる場合には、上記構成に加えて、上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する行の映像信号と同一内容の映像信号によって補間してもよい。

#### [0026]

当該構成では、補間対象のフィールドを構成する行の映像信号と同一内容の映像信号によって、他のフィールドのうち、当該行に連続する行を補間している。

したがって、1行分の映像信号を記憶し、当該行分の映像信号を複数回出力する だけで、行間を補間でき、回路構成を簡略化できる。

### [0027]

一方、上記1フレームが2フィールドから構成されている場合は、同一内容の映像信号で補間する代わりに、上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する2つの行の映像信号を平均した映像信号によって補間してもよい。

# [0028]

当該構成では、補間対象のフィールドの前の行と現在の行とを平均することで、両者の間の行を生成する。したがって、同一内容の映像信号で補間する場合よりも滑らかな映像を表示できる。さらに、他の映像信号を参照する場合、あるいは、上記2つの行に基づく場合であっても、平均以外の演算を用いて生成する場合と比較して、簡単な回路構成で補間できる。この結果、比較的簡単な回路構成で、より表示品質の良い表示装置を実現できる。

# [0029]

さらに、上記1フレームが2フィールドから構成されている場合は、他の補間 方法として、上記両補間工程の少なくとも1つでは、他のフィールドを構成する 各行の映像信号を補間する際、補間する行に連続する行であって、しかも、補間 対象のフィールドを構成する2つの行の映像信号に基づいて、補間する行の映像 信号を生成すると共に、上記2つの行の一方を構成する複数の画素への映像信号 と、他方を構成する複数の画素への映像信号とに基づいて、補間する行の1つの 画素への映像信号を生成してもよい。

#### [0030]

当該構成では、補間対象のフィールドの2行のうちの一方を構成する複数の画素への映像信号と、他方を構成する複数の画素への映像信号とに基づいて、補間する行の1画素への映像信号が生成されるので、同一内容の映像信号によって補間する場合や平均によって補間する場合よりも滑らかに、補間対象のフィールドの各行間を補間できる。この結果、より表示品質の良い表示装置を実現できる。

# [0031]

また、上記1フレームが2フィールドから構成されている場合は、他の補間方法として、上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する2つの行の映像信号と、補間対象に隣接するフィールドの映像信号とに基づいて補間してもよい。

# [0032]

当該構成では、補間対象のフィールドの映像信号だけではなく、補間対象に隣接するフィールドの映像信号も参照して、補間対象のフィールドの各行間が補間されるため、より滑らかに補間対象のフィールドの各行間を補間できる。この結果、より表示品質の良い表示装置を実現できる。

# [0033]

さらに、補間方法に拘わらず、上記構成に加えて、1フレームは、2フィールドから構成されており、2フィールド前の映像信号と、現フィールドの映像信号との比較結果を参照して、上記変調工程における変調の程度を調整する調整工程を含んでいてもよい。

#### [0034]

ところで、補間方法に拘わらず、上記表示装置の駆動方法では、前フィールドの映像信号を参照しているものの、基本的には、現フィールドの映像信号に基づいて、1フレーム分の映像を表示する画素群が駆動されている。したがって、フレーム単位で比較すると、同じ階調に保たれている画素であっても、補間後の前フィールドの映像信号と補間後の現フィールドの映像信号とが相違する可能性がある。

#### [0035]

ここで、前フィールドの映像信号と現フィールドの映像信号とが相違していても、画素の応答速度が遅ければ、フリッカーとして認識されることがないが、上記変調工程によって、階調遷移が強調され、画素の応答速度が向上していると、画素の不所望な往復駆動に起因するフリッカーが、表示装置のユーザに認識される虞れがある。

# [0036]

これに対して、上記構成では、2フィールド前の映像信号と現フィールドの映像信号との比較結果を参照して、上記変調工程における変調の程度を調整している。したがって、比較結果に応じて上記変調工程における変調の程度を調整することによって、画素の往復駆動時の階調遷移量を抑制できる。この結果、フリッカーの発生を防止でき、表示装置の表示品質を向上できる。

## [0037]

上記構成に加えて、上記調整工程では、2フィールド前の映像信号と現フィールドの映像信号とが概ね同じであれば、上記変調工程における変調を阻止してもよい。当該構成では、上記両映像信号が概ね同じであれば、変調が阻止されるので、往復駆動が発生しても、階調遷移量が最小限に保たれる。この結果、フリッカーの発生を防止でき、表示装置の表示品質を向上できる。

### [0038]

また、上記調整工程では、2フィールド前の映像信号と現フィールドの映像信号との差が予め定められた範囲であれば、両者の差に応じて、変調を抑制する程度を、変調を抑制しないレベルから、変調を阻止するレベルにまで徐々に変化させてもよい。

#### [0039]

当該構成では、2フィールド前の映像信号と現フィールドの映像信号との差が 予め定められた範囲であれば、変調を抑制する程度が両映像信号の差に応じて、 徐々に変化する。したがって、変調抑制の程度の変化が映像に顕れてしまい、表 示品位を低下させてしまうという現象の発生を防止できる。

#### [0040]

また、上記調整工程を設ける代わりに、上記変調工程では、前フィールドから 現フィールドへの階調遷移を強調するように、上記画素群の駆動信号が変調され ており、さらに、上記変調工程における階調遷移強調の程度は、第1の階調から 第2の階調への階調遷移を最も強調したときの応答速度と、第2の階調から第1 の階調への階調遷移を最も強調したときの応答速度とのうちの速い方を、遅い方 に近づけることによって、ある画素の前フィールドから現フィールドへの階調遷 移が、上記第1の階調から第2の階調への階調遷移と第2の階調から第1の階調への階調遷移とを繰り返すときに、当該画素の時間的積分輝度が上記第1の階調から第2の階調までの間の値になるように設定されていてもよい。

# [0041]

ところで、階調遷移を強調する程度は、駆動回路の回路構成や画素の駆動方法、あるいは、映像信号として表現可能な階調の範囲などによって制限されており、階調遷移を最も強調した場合、第1の階調から第2の階調へ階調遷移する際の応答速度は、第2の階調から第1の階調へ階調遷移する際の応答速度と一致しないことが多い。一方、両者の応答速度が大きく異なっていると、ある画素が往復駆動されたときに、当該画素の時間的平均輝度が、上記両階調の間から外れ、周囲から浮いて見えてしまう。

# [0042]

これに対して、上記構成では、変調工程における階調遷移強調の程度が上記のように設定されている。したがって、前フィールドの映像信号を参照しているものの、基本的には、現フィールドの映像信号に基づいて、1フレーム分の映像を表示する画素群を駆動した結果、画素が第1の階調と第2の階調との間で、不所望に往復駆動される場合であっても、当該画素の時間的積分輝度は、上記両階調の間の値になる。

#### [0043]

したがって、各フィールド毎に、1フレーム分の画素群が駆動されることによって、輝度を増大し、前フィールドの映像信号を参照して駆動信号を変調することによって、画素の応答速度を向上できるにも拘わらず、往復駆動された画素が周囲から浮いて見えるという現象の発生を防止でき、表示装置の表示品質を向上できる。

#### [0044]

また、上記構成に加えて、上記変調工程では、上記変調工程における階調遷移 強調の程度が、各階調遷移のうち、最も強調しても一番遅い階調遷移の応答速度 に、他の階調遷移の応答速度が略一致するように、他の階調遷移強調の程度が抑 えて設定されていてもよい。

当該構成では、全ての階調間の応答速度が概ね等しくなるので、各階調間の応答速度がバラバラの場合に発生する不具合、すなわち、動いている物体を表示している際に、高速に応答する画素と低速に応答する画素とが混在すると、上記物体が透けて見えるという不具合の発生を防止できる。

## [0046]

一方、本発明に係る表示装置の駆動装置は、上記課題を解決するために、複数フィールドの映像信号から1フレームの映像が構成されるインタレース信号に基づいて、現フィールドの映像信号と前フィールドの映像信号とを生成する現および前フィールドの映像信号生成手段と、1フレームの映像を表示する画素群を駆動するための駆動信号として、上記現フィールド映像信号に応じた駆動信号であって、上記前フィールド映像信号に応じて変調された駆動信号を生成する駆動信号生成手段とを有する表示装置の駆動装置において、以下の手段を講じたことを特徴としている。

# [0047]

すなわち、上記現および前フィールドの映像信号生成手段は、前フィールドを構成する各行の間を補間して、上記前フィールド映像信号として、1フレーム分の前フィールド映像信号を生成する前フィールド補間手段と、現フィールドを構成する各行の間を補間して、上記現フィールド映像信号として、1フレーム分の現フィールド映像信号を生成する現フィールド補間手段とを備えている。また、上記駆動信号生成手段は、上記各画素の駆動信号を生成する際、上記前フィールド映像信号のうち、当該画素への駆動信号を生成するための映像信号を参照して、当該画素の駆動信号を変調する。

## [0048]

上記構成では、両フィールド補間手段の出力に基づいて、駆動信号生成手段が 駆動信号を生成するので、当該表示装置の駆動装置は、上述の表示装置の駆動方 法で表示装置の画素群を駆動できる。

# [0049]

したがって、上記表示装置の駆動方法と同様に、各フィールド毎に、1フレー

ム分の画素群が駆動されることによって、輝度を増大し、前フィールドの映像信号を参照して駆動信号を変調することによって、画素の応答速度を向上できるにも拘わらず、比較対象のズレに起因する誤変調が発生せず、表示品質の良い表示装置を実現できる。

# [0050]

さらに、上記構成では、前フィールドの映像信号を参照して変調しているので、変調によって画素の応答速度を向上できるにも拘わらず、前フレームの映像信号を参照して変調する場合よりも、変調に必要な記憶容量を削減できる。

## [0051]

また、上記構成に加えて、上記インタレース信号では、2フィールドの映像から1フレームの映像が構成されており、上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行分記憶し、1行分の映像信号を、上記インタレース信号のドットクロックの2倍の周波数で2回出力するラインメモリを備え、上記前フィールド補間手段は、現フィールドを構成する各行の映像信号を格納し、次のフィールドまで記憶するフィールドメモリと、上記ラインメモリの出力に基づいて、現フィールドを構成する各行の映像信号を上記フィールドメモリに格納すると共に、前のフィールドを構成する各行の映像信号を、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波数で2回出力させる制御手段とを備えていてもよい。

#### [0052]

当該構成では、前フィールドの映像データを出力するために必要なフィールドメモリが、前フィールド補間手段としても動作しており、当該フィールドメモリが、前フィールド映像信号として、前フィールドの1行分の映像データを2回出力している。したがって、前フィールド補間手段とフィールドメモリとを別に設けた構成、例えば、フィールドメモリがインタレース信号と同じ周波数で映像信号を出力し、フィールドメモリの後段に設けられたラインメモリが、フィールドメモリの出力を1行分記憶して、1水平ライン分の映像データを2回出力する構成と比較して、ラインメモリの数を削減できる。この結果、小さな回路規模で、表示装置の駆動装置を実現できる。

# [0053]

一方、フィールドメモリが前フィールド補間手段として動作する代わりに、上記インタレース信号では、2フィールドの映像から1フレームの映像が構成されており、上記現および前フィールドの映像信号生成手段は、上記インタレース信号を1フィールド分遅らせて出力するフィールドメモリを備え、上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行分記憶すると共に、当該1行分の映像信号を、上記インタレース信号のドットクロックの2倍の周波数で2回出力する現フィールドラインメモリを備え、上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリと同じ周波数で2回出力する前フィールドラインメモリを備えていてもよい。

### [0054]

当該構成では、フィールドメモリが前フィールド補間手段として動作する構成と比較して、フィールドメモリが出力する映像信号のドットクロックの周波数は、インタレース信号のドットクロックの周波数に抑えられている。したがって、フィールドメモリの動作周波数を抑制できる。この結果、比較的回路設計が容易で、EMI (Electro-Magnetic Interference)対策しやすい表示装置の駆動装置を実現できる。

#### [0055]

さらに、上記各構成に加えて、現フィールドの映像信号を、現フィールドと映像信号の位置が同一の近接するフィールドまで記憶し、同一位置フィールド映像信号として出力する同一位置フィールド映像信号生成手段を備え、上記駆動信号生成手段は、上記同一位置フィールド映像信号と現フィールド映像信号とを比較し、比較結果に応じて、前フィールドから現フィールドへの階調遷移強調の程度を変更して、駆動信号を生成してもよい。

#### [0056]

当該構成では、上記駆動信号生成手段が同一位置フィールド映像信号と現フィールド映像とを比較し、比較結果に応じて、前フィールドから現フィールドへの 階調遷移強調の程度を変更している。したがって、上述の表示装置の駆動方法の うち、比較結果に応じて階調遷移強調の程度を調整する駆動方法と同様に、比較 結果に応じて画素の往復駆動時の階調遷移量を抑制できる。この結果、フリッカ ーの発生を防止でき、表示装置の表示品質を向上できる。

### [0057]

また、上記インタレース信号では、2フィールドの映像から1フレームの映像 が構成されている場合、上記構成に加えて、以下の手段を備えていてもよい。す なわち、上記現フィールド補間手段は、現フィールドを構成する各行の映像信号 を1行分記憶し、1行分の映像信号を、上記インタレース信号のドットクロック の2倍の周波数で2回出力する現フィールドラインメモリを備えている。さらに 、表示装置の駆動装置には、現フィールドの映像信号を2つ後のフィールドまで 記憶するフィールドメモリと、当該フィールドメモリから、上記現フィールドラ インメモリと同じ周波数で、前フィールドの1行分の映像信号と前々フィールド の1行分の映像信号とを交互に出力させる制御手段と、上記フィールドメモリが 出力する前々フィールドの映像信号を1行分記憶すると共に、上記前々フィール ド映像信号として、上記現フィールドラインメモリと同じ周波数で当該1行分の 映像信号を2回出力する前々フィールドラインメモリとが設けられている。また 、上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1 行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリ と同じ周波数で2回出力する前フィールドラインメモリを備え、上記駆動信号生 成手段は、上記現フィールド補間手段が出力する現フィールド映像信号と上記前 々フィールド映像信号とを上記各画素毎に比較して、上記各画素毎に、比較結果 を出力する比較手段と、比較結果に基づいて、各画素の駆動信号の変調の程度を 調整する調整手段とを備えている。

### [0058]

当該構成では、前々フィールド映像信号生成手段のフィールドメモリが、前フィールドの映像信号と前々フィールドの映像信号とを交互に出力し、現および前フィールドの映像信号生成手段の前フィールド補間手段が、当該フィールドメモリの出力に基づいて前フィールド映像信号を生成している。

#### [0059]

したがって、上記フィールドメモリとは別に、前フィールドの映像信号を記憶 するフィールドメモリを設け前フィールド映像信号を生成する構成よりも少ない 記憶容量で表示装置の駆動装置を実現できる。

# [0060]

なお、上記フィールドメモリが出力する前フィールドおよび前々フィールドの映像信号は、それぞれ用のラインメモリによって、それぞれの行間が補間されるので、それぞれの映像信号を記憶するためのフィールドメモリが共用され、当該フィールドメモリがインタレース信号のドットクロックの2倍の周波数で、各映像信号を出力しているにも拘わらず、駆動信号生成手段は、前フィールド映像信号を正しく参照して、駆動信号を変調できると共に、比較手段は、各画素毎に前々フィールド映像信号と現フィールド映像信号とを比較できる。

# $[0\ 0\ 6\ 1]$

また、上記インタレース信号が2フィールドの映像から1フレームの映像が構 成されている場合には、フィールドメモリの出力する前々フィールドの映像信号 を補間する代わりに、以下の構成を備えていてもよい。すなわち、上記現フィー ルド補間手段は、現フィールドを構成する各行の映像信号を1行分記憶し、1行 分の映像信号を、上記インタレース信号のドットクロックの 2 倍の周波数で 2 回 出力する現フィールドラインメモリを備えている。さらに、表示装置の駆動装置 には、現フィールドの映像信号を2つ後のフィールドまで記憶するフィールドメ モリと、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波 数で、前フィールドの1行分の映像信号と前々フィールドの1行分の映像信号と を交互に出力させる制御手段とが設けられている。また、上記前フィールド補間 手段は、上記フィールドメモリが出力する映像信号を1行分記憶すると共に、当 該1行分の映像信号を、上記現フィールドラインメモリと同じ周波数で2回出力 する前フィールドラインメモリを備え、上記駆動信号生成手段は、上記現フィー ルド補間手段が出力するフィールド映像信号を構成する各行の映像信号のうち、 1 行おきの映像信号と、上記前々フィールド映像信号とを上記各画素毎に比較し て、上記各画素毎に、比較結果を出力する比較手段と、比較結果を1行分記憶す ると共に、1行分の比較結果を、上記現フィールドラインメモリと同じ周波数で

2回出力する比較結果ラインメモリと、当該比較結果ラインが出力する各画素の 比較結果に応じて、当該画素の駆動信号の変調の程度を調整する調整手段とを備 えていてもよい。

# [0062]

当該構成では、フィールドメモリの出力する前々フィールドの映像信号の行間を前々フィールドラインメモリが補間する代わりに、比較結果ラインメモリが、比較結果の行間を補間している。ここで、多くの場合、比較結果の記憶に必要な記憶容量は、映像データ自体の記憶に必要な記憶容量よりも少ない。したがって、前々フィールドの映像信号自体ではなく、比較結果の行間を補間することによって、表示装置の駆動装置に必要な記憶容量を削減でき、回路規模を縮小できる

# [0063]

なお、前々フィールドは、1フレーム前のフィールドなので、前々フィールド を構成する各行は、現フィールドを構成する各行と同じ位置の行である。したが って、比較結果を補間したとしても、比較対象がズレることはなく、調整手段は 、何ら支障なく、当該画素の駆動信号の変調の程度を調整できる。

#### [0064]

また、本発明に係るプログラムは、上述の各工程をコンピュータに実行させるプログラムである。したがって、当該プログラムがコンピューで実行されると、当該コンピュータは、表示装置を上記駆動方法で駆動できる。この結果、上記表示装置の駆動方法と同様に、各フィールド毎に、1フレーム分の画素群が駆動されることによって、輝度を増大し、前フィールドの映像信号を参照して駆動信号を変調することによって、画素の応答速度を向上できるにも拘わらず、比較対象のズレに起因する誤変調が発生しない。この結果、表示品質の良い表示装置を実現できる。

# [0065]

#### 【発明の実施の形態】

#### 〔第1の実施形態〕

本発明の一実施形態について図1ないし図6に基づいて説明すると以下の通り

である。すなわち、本実施形態に係る画像表示装置(表示装置)1は、各フィールド毎に1フレーム分の画素群を駆動することによって輝度を増大すると共に、前フィールドの映像信号を参照して駆動信号を変調することによって画素の応答速度を向上しているにも拘わらず、演算対象のズレに起因する誤変調の発生を防止可能な画像表示装置1である。

# [0066]

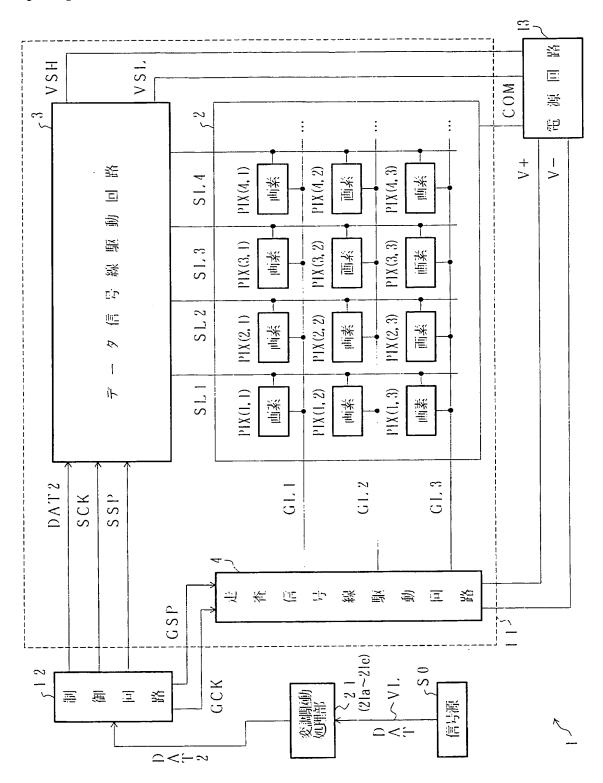

当該画像表示装置1のパネル11は、図2に示すように、マトリクス状に配された画素PIX(1,1) ~PIX(n,m) を有する画素アレイ2と、画素アレイ2のデータ信号線SL1~SLnを駆動するデータ信号線駆動回路3と、画素アレイ2の走査信号線GL1~GLmを駆動する走査信号線駆動回路4とを備えている。また、画像表示装置1には、両駆動回路3・4へ制御信号を供給する制御回路12と、入力される映像信号に基づいて、上記階調遷移を強調するように、上記制御回路12へ与える映像信号を変調する変調駆動処理部21とが設けられている。なお、これらの回路は、電源回路13からの電力供給によって動作している。

# [0067]

以下では、変調駆動処理部21の詳細構成について説明する前に、画像表示装置1全体の概略構成および動作を説明する。また、説明の便宜上、例えば、i番目のデータ信号線SLiのように、位置を特定する必要がある場合にのみ、位置を示す数字または英字を付して参照し、位置を特定する必要がない場合や総称する場合には、位置を示す文字を省略して参照する。

#### [0068]

上記画素アレイ 2 は、複数(この場合は、n本)のデータ信号線  $SL1 \sim SL$  n と、各データ信号線  $SL1 \sim SL$  n に、それぞれ交差する複数(この場合は、m本)の走査信号線  $GL1 \sim GLm$  とを備えており、1 からn までの任意の整数 および 1 からm までの任意の整数を j とすると、データ信号線 SLi および走査 信号線 GLj の組み合わせ毎に、画素 PIX(i,j) が設けられている。

#### [0069]

本実施形態の場合、各画素PIX(i,i)は、隣接する2本のデータ信号線SL

(i-1) ・SLiと、隣接する2本の走査信号線GL(j-1) ・GLjとで囲まれた部分に配されている。

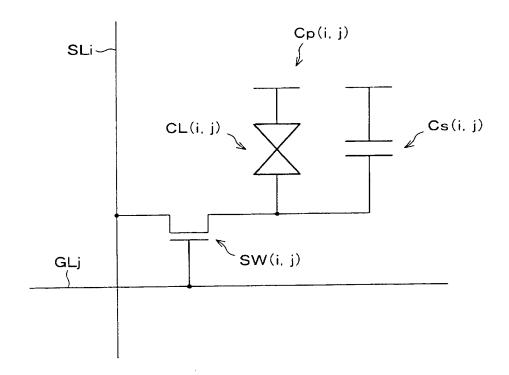

### [0070]

一例として、画像表示装置 1 が液晶表示装置の場合について説明すると、上記画素 P I X(i,j) は、例えば、図 3 に示すように、スイッチング素子として、ゲートが走査信号線 G L j へ、ドレインがデータ信号線 S L i に接続された電界効果トランジスタ S W(i,j) と、当該電界効果トランジスタ S W(i,j) のソースに、一方電極が接続された画素容量 C p(i,j) とを備えている。また、画素容量 C p(i,j) の他端は、全画素 P I X …に共通の共通電極線に接続されている。上記画素容量 C p(i,j) は、液晶容量 C L(i,j) と、必要に応じて付加される補助容量 C S(i,j) とから構成されている。

# [0071]

# [0072]

本実施形態に係る上記液晶表示装置は、液晶セルとして、垂直配向モードの液晶セル、すなわち、電圧無印加時には、液晶分子が基板に対して略垂直に配向し、画素PIX(i,x)の液晶容量CL(i,j)への印加電圧に応じて、液晶分子が垂直配向状態から傾斜する液晶セルを採用しており、当該液晶セルをノーマリブラックモード(電圧無印加時には、黒表示となるモード)で使用している。

# [0073]

上記構成において、図2に示す走査信号線駆動回路4は、各走査信号線GL1

$\sim$  G L mへ、例えば、電圧信号など、選択期間か否かを示す信号を出力している。また、走査信号線駆動回路 4 は、選択期間を示す信号を出力する走査信号線 G L j を、例えば、制御回路 1 2 から与えられるクロック信号 G C K やスタートパルス信号 G S P などのタイミング信号に基づいて変更している。これにより、各走査信号線 G L 1  $\sim$  G L m は、予め定められたタイミングで、順次選択される。

# [0074]

さらに、データ信号線駆動回路 3 は、映像信号 D A T として、時分割で入力される各画素 P I X …への映像データ D …を、所定のタイミングでサンプリングすることで、それぞれ抽出する。さらに、データ信号線駆動回路 3 は、走査信号線駆動回路 4 が選択中の走査信号線 G L j に対応する各画素 P I X (n,j) へ、各データ信号線 S L 1  $\sim$  S L n を介して、それぞれへの映像データ D …に応じた出力信号を出力する。

# [0075]

なお、データ信号線駆動回路3は、制御回路12から入力される、クロック信号SCKおよびスタートパルス信号SSPなどのタイミング信号に基づいて、上記サンプリングタイミングや出力信号の出力タイミングを決定している。

# [0076]

一方、各画素  $PIX(1,j) \sim PIX(n,j)$  は、自らに対応する走査信号線 GL j が選択されている間に、自らに対応するデータ信号線  $SL1 \sim SLn$  に与えられた出力信号に応じて、発光する際の輝度や透過率などを調整して、自らの明るさを決定する。

#### [0077]

ここで、走査信号線駆動回路 4 は、走査信号線  $GL1 \sim GLm$  を順次選択している。したがって、画素アレイ 2 の全画素  $PIX(1,1) \sim PIX(n,m)$  を、それぞれへの映像データ D が示す明るさに設定でき、画素アレイ 2 へ表示される画像を更新できる。

# [0078]

本実施形態に係る画像表示装置1は、インタレースの映像信号DATを表示する表示装置であって、映像信号源SOから変調駆動処理部21へ与えられる映像

信号DATは、1フレームを複数のフィールド(例えば、2フィールド)に分割すると共に、当該フィールド単位で伝送されている。

### [0079]

具体的には、信号源S0は、映像信号線VLを介して、画像表示装置1の変調 駆動処理部21に映像信号DATを伝送する際、あるフィールドF(k) 用の映像 データを全て伝送した後に、次のフィールドF(k+1) 用の映像データを伝送する などして、各フィールド用の映像データを時分割伝送している。

# [0080]

# [0081]

本実施形態では、2フィールドから1フレームを構成しており、偶数フィールドでは、1フレームを構成する各水平ラインのうち、偶数行目の水平ラインの映像データが伝送される。また、奇数フィールドでは、奇数行目の水平ラインの映像データが伝送される。

## [0082]

さらに、上記信号源S0は、1水平ライン分の映像データD(\*, j, k)を伝送する際も上記映像信号線VLを時分割駆動しており、予め定められた順番で、各映像データが順次伝送される。

#### [0083]

また、本実施形態では、映像信号源S0からの映像信号DATがインタレース 信号であるにも拘わらず、画像表示装置1は、現フィールドの映像データに基づ いて、画素アレイ2の全画素PIXを駆動している。また、画像表示装置1の変 調駆動処理部21は、現フィールドの映像データに基づいて各画素PIXへの駆 動信号を生成する際、前フィールドの映像データを参照し、前フィールドから現 フィールドへの階調遷移を強調するように、駆動信号を変調している。

# [0084]

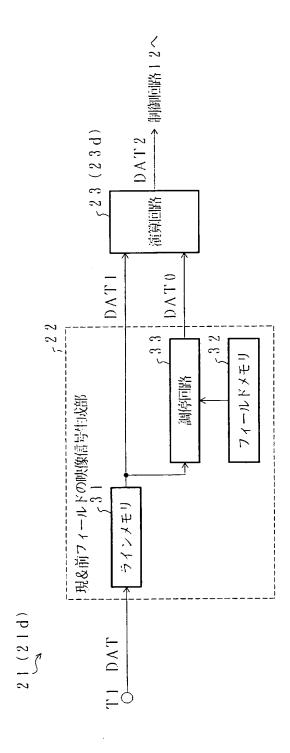

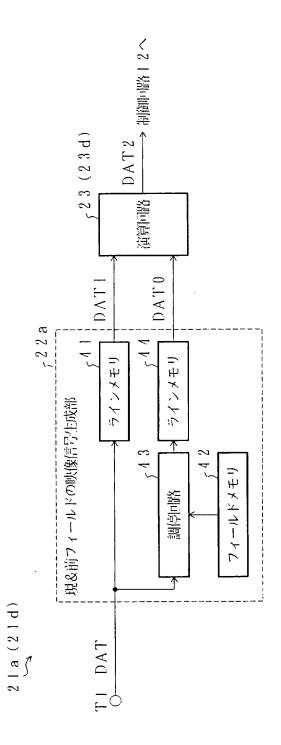

より詳細には、本実施形態に係る変調駆動処理部21は、図1に示すように、インタレースの映像信号DATに基づいて、現フィールドの映像データからなる現フィールド映像信号DAT1を出力すると共に、現フィールドの映像データを次フィールドまで記憶し、当該記憶された映像データに基づいて、前フィールドの映像データからなる前フィールド映像信号DAT0を出力する現&前フィールドの映像信号生成部22と、両フィールド映像信号DAT0・DAT1に基づいて、前フィールドから現フィールドへの階調遷移を強調するように、現フィールドの映像信号を変調した信号(補正映像信号DAT2)を生成し、当該補正映像信号DAT2を出力する演算回路23とを備えている。

### [0085]

上記構成では、フィールド毎に全画素PIXを駆動しているので、現フィールド以外のフィールドに対応する画素PIXを暗表示にする場合よりも、画像表示装置1全体の輝度を向上できる。なお、画像表示装置1が光源(バックライトなど)を有する液晶表示装置の場合、光源は、暗表示中も点灯しており、当該光源からの光がユーザに到達することを、画素PIXが妨げることによって、暗表示する。この結果、暗表示しても、明表示と同程度の電力を消費する。したがって、フィールド毎に全画素PIXを駆動することによって、電力消費を余り増加させずに、画像表示装置1全体の輝度を向上でき、特に好適である。

# [0086]

また、上記構成では、前フィールドから現フィールドへの階調遷移が強調されるので、応答速度が比較的遅い画素PIXを利用している場合であっても、画像表示装置1の応答速度を向上できる。さらに、前フィールドの映像データを参照しているものの、基本的には、現フィールドの映像データに基づいて、画素アレイ2の全画素PIXを駆動している。したがって、階調遷移の強調によって応答速度を向上しているにも拘わらず、前フレームの映像データを参照して、現フレームの駆動信号を変調する構成に比べて、画像表示装置1が記憶すべき映像データの数を削減でき、比較的小さな回路規模で画像表示装置1を実現できる。

### [0087]

さらに、本実施形態に係る変調駆動処理部21では、現フィールドの映像データを、前フィールドの映像データに応じて変調することによって、応答速度向上と回路規模の削減との双方を実現しているにも拘わらず、参照先の不一致に起因する誤変調を避けるために、演算回路23の後段ではなく、前段の回路(例えば、現&前フィールドの映像信号生成部22)において、前フィールドの映像データの補間と現フィールドの映像データの補間とを行っている。

# [0088]

具体的には、本実施形態に係る現&前フィールドの映像信号生成部22は、インタレースの映像信号DATとして印加される映像データを1水平ライン分蓄積した後、2倍の周波数で1水平ライン分の映像データを2回出力するラインメモリ31と、現フィールドの各映像データを次のフィールドまで記憶するフィールドメモリ32と、当該ラインメモリ31の出力に基づいて、現フィールドの各映像データをフィールドメモリ32に記憶された各映像データの1水平ライン分を、上記ラインメモリ31と同じ周波数で2回読み出して出力する調停回路33とを備え、上記ラインメモリ31および調停回路33の出力は、それぞれ、各フィールド映像信号DAT1・DAT0として、演算回路23に入力されている。

#### [0089]

さらに、演算回路 23 は、上記両フィールド映像信号DAT 0・DAT 1 に基づいて補正映像信号DAT 2 を生成する際、互いに同じ画素 P I X(i,j) に対応する映像データ D(i,j,k-1) および D(i,j,k) に基づいて、当該画素 P I X(i,j) )へ供給される、補正後の映像データ、すなわち、補正映像データ D 2(i,j,k) を生成する。

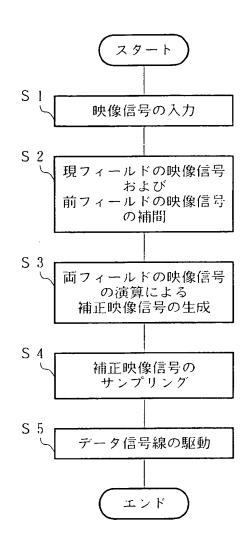

#### [0090]

上記構成では、図4に示すステップ1(以下では、S1のように略称する)に おいて、映像信号DATが現&前フィールドの映像信号生成部22へ入力される と、当該映像信号生成部22は、S2において、現フィールドF(k)の映像デー タの水平ライン間を補間して、現フィールド映像信号DAT1を生成する。また 、上記S2において、上記映像信号生成部22は、予め記憶していた前フィールドF(k-1)の映像データに基づき、当該映像データの水平ライン間を補間して、前フィールド映像信号DAT0を生成する。

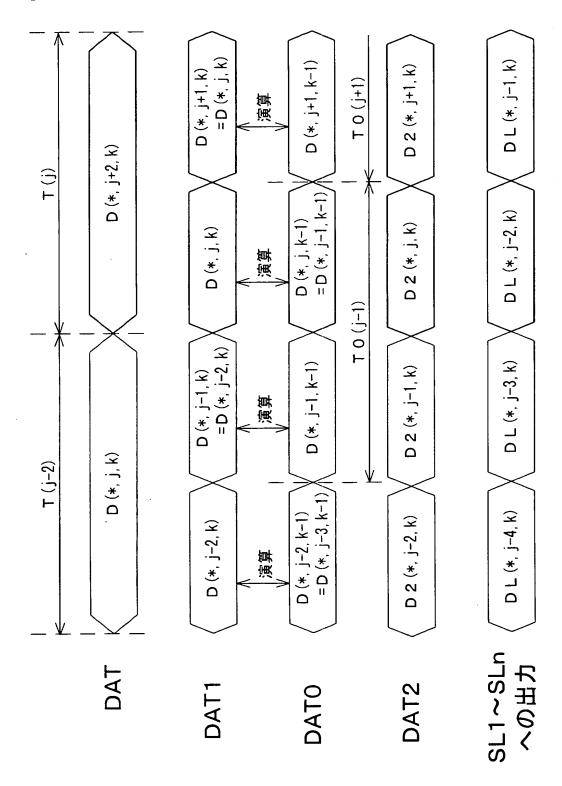

# [0091]

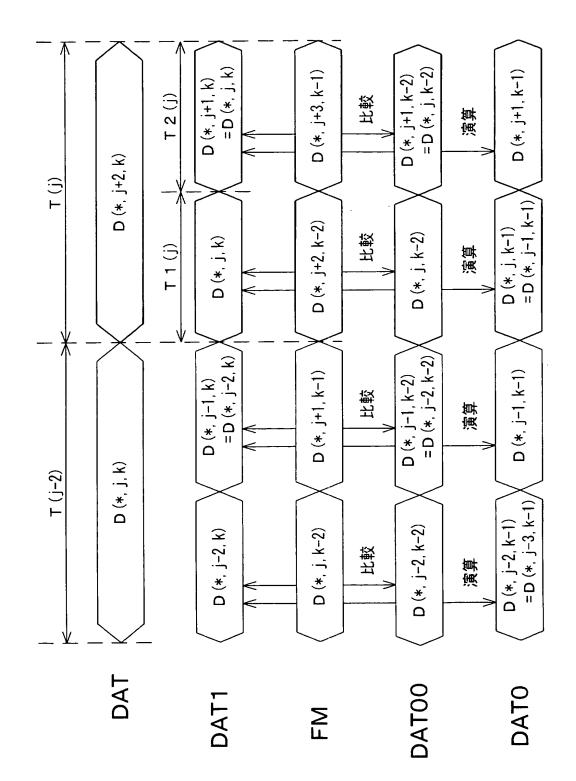

例えば、本実施形態では、図5に示すように、1水平ライン分の映像データを2回出力することによって、水平ライン間を補間している。また、図5では、一例として、現&前フィールドの映像信号生成部22が映像信号DATの1水平ライン分遅れて、現フィールド映像信号DAT1を出力する例を示している。

## [0092]

したがって、期間 T(j-2) において、現&前フィールドの映像信号生成部 2 2 に入力された映像データ D(\*,j,k) は、期間 T(j) に、現フィールド映像信号 D(\*,j,k) 、および、映像データ D(\*,j+1,k) として出力される。

### [0093]

また、現&前フィールドの映像信号生成部 2 2 は、前フィールドF (k-1) において、蓄積した映像データに基づき、当該映像データの水平ライン間を補間して、前フィールド映像信号 DAT 0 を生成している。したがって、上記期間 T(j) において、映像信号生成部 2 2 は、前フィールド映像信号 DAT 0 として、映像データ D(\*,j,k-1) 、および、映像データ D(\*,j+1,k-1) を出力する。

#### [0094]

## [0095]

さらに、上記S3にて、変調駆動処理部21の演算回路23が補正映像信号DAT2を生成すると、データ信号線駆動回路3は、次のフィールドF(k+1)において、当該補正映像信号DAT2をサンプリングして、補正映像信号DAT2の

各映像データD 2 (\*, j, k) を抽出する(S 4)。さらに、データ信号線駆動回路 3 は、S 5 において、上記S 4 にてサンプリングした各映像データD 2 (\*, j, k) に応じた駆動信号D L (\*, j, k) を、各データ信号線S L 1 ~ S L n ~ 出力する。これにより、画像表示装置 1 の画素アレイ 2 には、映像信号D A T が示す画像が表示される。なお、図 5 では、一例として、データ信号線駆動回路 3 が補正映像信号D A T 2 から補正映像信号D A T 2 の 2 水平ライン分遅れて、各駆動信号D L (\*, j, k) を出力する場合を示している。

## [0096]

ここで、図22に示すように、補正後に補間する構成では、ある補正映像データを生成するための映像データの対は、補間によって生成される他の補正映像データを生成するための映像データの対と一致してしまう。

# [0097]

一方、1フレームを複数のフィールドに分割して伝送する場合、そのフィールドにおいて伝送される水平ラインの位置は、連続して伝送されるフィールド間で互いに異なっているため、補間の際に基準となる水平ラインも、各フィールド間で変化する。したがって、フレームを構成する各水平ラインのうち、互いに同じ水平ラインを参照して補間される水平ラインの組同士の境界線も、各フィールド間で変化する。

# [0098]

これらの結果、あるフィールドにおいて、ある水平ラインの補正映像データを 正しく生成可能な映像データの対を選択したとしても、当該映像データの対に基 づいて生成される補正映像データを補間することによって生成された補正映像デ ータの中には、当該映像データ対以外の映像データ対に基づいて生成すべき補正 映像データが含まれてしまう。

#### [0099]

例えば、図 2 4 に示す、ある奇数フィールドF(k-1) では、ある奇数をjとするとき、水平ラインL(j) の映像データD(\*,j,k-1) に基づいて、次の水平ラインL(j+1) の映像データD(\*,j+1,k-1) が生成されるのに対して、次の偶数フィールドF(k) では、水平ラインL(j-1) の映像データD(\*,j-1,k) に基づいて、

水平ラインL(j) の映像データD(\*,j,k) が生成されている。なお、図24では、基準となる映像データが同じ水平ライン同士を、太線で囲っている。

# [0100]

したがって、上記偶数フィールドF(k) において、上記水平ラインL(j) の補正映像データD(i,j,k) は、映像データD(i,j,k-1) = D(i,j+1,k-1) と、映像データD(i,j,k) = D(i,j-1,k) に基づいて生成すべきであるにも拘わらず、当該偶数フィールドF(k) において、次の水平ラインL(j+1) の補正映像データD(i,j+1,k) は、映像データD(i,j+1,k-1) = D(i,j,k-1) と、映像データD(i,j+1,k) は、映像データD(i,j+1,k-1) = D(i,j,k-1) と、映像データを正しく生成するために必要な映像データ対の内容は、互いに異なっている。

### [0101]

この結果、補正後に補間する構成では、例えば、上記水平ラインL(j) の補正映像データD(i,j,k) が正しく生成できるように、映像データD(i,j,k-1) とD(i,j-1,k) とに基づいて、補正映像データD(i,j,k) を生成すると、次の水平ラインL(j+1) の補正映像データD(i,j+1,k) は、正しく生成できなくなってしまう。

# [0102]

これに対して、本実施形態では、演算回路23による補正映像信号DAT2の 生成前に水平ライン間が補間されているので、演算回路23は、各補正映像データのそれぞれについて、両フィールド映像信号DAT0・DAT1を構成する映像データの中から当該補正映像データを正しく生成するための映像データの対を 選択できる。

# [0103]

例えば、図5の期間T(j-2)の間、現フィールド映像信号DAT1では、映像データD(\*,j-2,k) およびD(\*,j-1,k) として、ある水平ラインL(j-2)の映像データD(\*,j-,k) が2回出力され、期間T(j)の間、映像データD(\*,j,k) およびD(\*,j+1,k) として、ある水平ラインL(j) の映像データD(\*,j,k) が2回出力されている。一方、前フィールド映像信号DAT0では、当該期間T(j) と比較して、現&前フィールドの映像信号生成部22が1水平ライン分の映像デー

タを 1 回出力する期間だけ前の期間 T 0 (j-1) の間、映像データ D (\*, j-1, k-1) および D (\*, j, k-1) として、ある水平ライン L (j-1) の映像データ D (\*, j-1, k) が 2 回出力されており、同じ分だけ後の期間 T 0 (j+1) の間、映像データ D (\*, j+1, k-1) および D (\*, j+2, k-1) として、ある水平ライン L (j+1) の映像データ D (\*, j+1, k) が 2 回出力されている。

# [0104]

さらに、演算回路 2 3 は、前フィールド映像信号 D A T 0 の映像  $\vec{r}$   $\vec{r}$

### [0105]

ここで、上記期間 T(j) と、期間 T(j) および T(j) および T(j) および T(j) において、現フィールド映像信号 DAT1 では、互いに同じ内容の映像 データ D(\*,j,k) と D(\*,j+1,k) とが出力されているのに対して、前フィールド映像信号 DAT0 では、期間 T(j) の前半に出力される映像 データ D(\*,j,k-1) の内容、すなわち、D(\*,j-1,k-1) の内容と、後半に出力される映像 データ D(\*,j+1,k) の内容とが互いに異なっている。

# [0106]

ところが、上記構成では、補間後に補正しているので、前半と後半とで互いに 異なる映像データを参照して、現フィールド映像信号DAT1に応じた駆動信号 を変調する場合であっても、双方で、正しく階調遷移を強調する変調が可能にな る。この結果、補正後に補間する構成と異なり、参照先の不一致に起因する誤変 調が発生せず、当該誤変調による画像表示装置1の表示品位の低下を防止できる

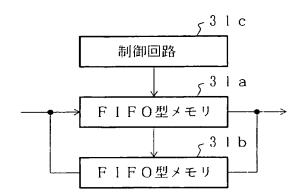

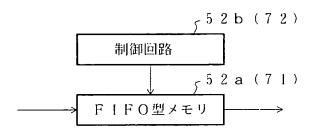

### [0107]

以下では、ラインメモリ31およびフィールドメモリ32のさらに詳細な構成の一例について説明する。すなわち、本実施形態に係るラインメモリ31は、FIFO (First In First Out) 型のメモリとして実現されており、入力された映

像信号DATのドットクロックの周波数が13.5 [MHz]とすると、27 [MHz] の周波数で映像データを出力する。当該構成では、1水平ライン分の映像データを、入力されたときの半分の時間で出力できるので、1水平ライン分の映像データを2回出力しているにも拘わらず、1水平ライン分の映像データを入力する周期と、1水平ライン分の映像データを2回ずつ出力する周期とが一致している。この結果、両者の相違に起因するオーバーフローが発生せず、ラインメモリ31は、上述の図5に示すように、何ら支障なく、1水平ライン分の映像データを2回出力できる。

# [0108]

上記ラインメモリ31は、例えば、図6に示すように、それぞれ1水平ライン 分の映像データを蓄積可能な2ラインのFIFO型メモリ31a・31bと、入 力される各映像データを両ラインの一方へ順次蓄積させると共に、当該ラインの FIFO型メモリへ1水平ライン分の映像データが入力される間に、他方のラインのFIFO型メモリから1水平ライン分の映像データを2回出力させ、さらに、1水平ライン分の映像データの入力が終了すると、両ラインの役割を交換する 制御回路31cとを備えている。

# [0109]

一方、上記フィールドメモリ32には、調停回路33によって、ラインメモリ31から出力される映像データが1フィールド分蓄積され、調停回路33は、次のフィールドにおいて、フィールドメモリ32に蓄積された前フィールドの映像データを出力できる。

#### [0110]

本実施形態に係るラインメモリ31は、1水平ライン分の映像データを2回出力しているので、本実施形態に係る調停回路33は、フィールドメモリ32に1水平ライン分の映像データを蓄積した後、例えば、次の水平ラインの映像データの蓄積を休止したり、次の水平ラインの映像データを、前の水平ラインの映像データが記憶された記憶領域に上書きするなどして、1フィールド分の映像データをフィールドメモリ32に記憶している。これにより、上記ラインメモリ31が、1水平ライン分の映像データと同じ内容の映像データを再度出力しているにも

拘わらず、フィールドメモリ32の記憶容量は、1フィールド分の映像データの 蓄積に十分な容量に抑えられている。

#### [0111]

さらに、上記調停回路33は、前フィールドの映像データを出力する際、上記 ラインメモリ31が映像データを出力する場合と同じ周波数で、1水平ライン分 の映像データを出力した後、当該映像データを、次の水平ライン分の映像データ として再度出力する。

## [0112]

上記構成では、ある水平ラインの映像データと次の水平ラインの映像データとが、上記ラインメモリ31が映像データを出力する場合と同じ周波数で出力されるので、ラインメモリ31に1水平ライン分の映像データが入力される周期と、調停回路33が1水平ライン分の映像データを2回ずつ出力する周期とが一致している。この結果、両者の相違に起因するオーバーフローが発生せず、調停回路33は、上述の図5に示すように、何ら支障なく、前フィールドの映像データとして、1水平ライン分の映像データを2回出力できる。

#### $[0\ 1\ 1\ 3\ ]$

## [第2の実施形態]

上記第1の実施形態では、ラインメモリ31の出力に基づいて、フィールドメモリ32へ現フィールドの映像データが蓄積される構成について説明した。これに対して、本実施形態では、ラインメモリ31と同様に、映像信号DATに基づいて、現フィールドの映像データがフィールドメモリ32へ蓄積される構成について説明する。

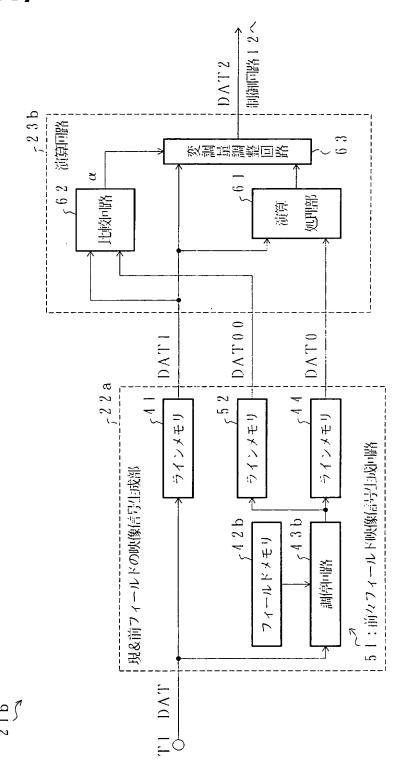

#### [0114]

すなわち、本実施形態に係る変調駆動処理部 2 1 a では、図 7 に示すように、現&前フィールドの映像信号生成部 2 2 に代えて現&前フィールドの映像信号生成部 2 2 a は、第 1 の実施形態に 係るラインメモリ 3 1 と同様の構成のラインメモリ 4 1 と、現フィールドの各映像データを次のフィールドまで記憶するフィールドメモリ 4 2 と、映像信号 D A Tに基づいて、現フィールドの各映像データをフィールドメモリ 4 2 に書き込む

と共に、次のフィールドにおいて、フィールドメモリ42に蓄積された各映像データを映像信号DATと同じ周波数で読み出して出力する調停回路43と、ラインメモリ41と同様の構成で、フィールドメモリ42の出力を入力とするラインメモリ44とを備えている。

## [0115]

当該構成では、ラインメモリ41は、上記ラインメモリ31と同様に、水平ライン間が補間された現フィールド映像信号DAT1を出力する。また、ラインメモリ44は、前フィールドの映像データであって、映像信号DATと同じ周波数で調停回路43から出力される映像データに基づいて、上記ラインメモリ31と同様に、前フィールドの水平ライン間を補間する。これにより、ラインメモリ44は、第1の実施形態に係る現&前フィールドの映像信号生成部22と同様に、水平ライン間が補間された前フィールド映像信号DAT0を出力できる。

#### [0116]

当該構成でも、第1の実施形態と同様に、演算回路23による補正映像信号DAT2の生成前に水平ライン間が補間されており、演算回路23は、各補正映像データのそれぞれについて、両フィールド映像信号DAT0・DAT1を構成する映像データの中から当該補正映像データを正しく生成するための映像データの対を選択し、当該映像データ対に基づいて、補正映像データを生成する。

#### $[0\ 1\ 1\ 7]$

したがって、第1の実施形態と同様に、補正映像データの生成時における参照 先の不一致、および、当該不一致に起因する誤変調が発生せず、当該誤変調によ る画像表示装置1の表示品位の低下を防止できる。

#### [0118]

さらに、本実施形態では、第1の実施形態とは異なり、調停回路43が映像信号DATに基づいて、現フィールドの映像データをフィールドメモリ42へ記憶し、フィールドメモリ42の後段に設けたラインメモリ44によって水平ライン間が補間されている。したがって、第1の実施形態のように、調停回路(33)がラインメモリ(31)の出力に基づいて現フィールドの映像データをフィールドメモリ(32)へ記憶する構成に比べて、調停回路43およびフィールドメモ

リ42の動作周波数を下げることができる。

#### [0119]

例えば、映像信号DATにおける映像データの周波数(ドットクロック)が13.5  $\{MHz\}$  とすると、第1の実施形態の場合、現&前フィールドの映像信号生成部22を構成するラインメモリの数が1つですむ代わりに、フィールドメモリ32に入力される映像データの周波数、および、フィールドメモリ32が出力する映像データの周波数は、それぞれ27  $\{MHz\}$  になる。したがって、フィールドメモリ32が入出力を同時に、すなわち、入力および出力をそれぞれの周波数で処理するためには、フィールドメモリ32は、54  $\{MHz\}$  で動作する必要がある。これに対して、本実施形態の構成では、フィールドメモリ42の入出力周波数は、それぞれ、13.5  $\{MHz\}$  なので、フィールドメモリ42の動作周波数を27  $\{MHz\}$  にまで抑えることができる。この結果、比較的容易に回路設計可能で、しかも、比較的容易にEMIノイズの発生を抑えることができる。

## [0120]

#### 「第3の実施形態]

ところで、第1および第2の実施形態に係る画像表示装置1は、前フィールドから現フィールドへの階調遷移を強調するように、現フィールドの映像データに応じた駆動信号を変調することによって、画素PIXの応答速度を向上させているが、基本的には、現フィールドの映像データに基づいて、現フィールドの映像データに対応する画素PIXだけではなく、他のフィールドの映像データに対応する画素PIXも駆動している。

## [0121]

したがって、例えば、静止画を表示している場合など、前フレームと現フレームとの間で、互いに同一の画素PIXに対応する映像データ同士を比較したときに殆ど差がない場合であっても、当該画素PIXは、前フィールドの映像データによっても駆動されている。また、変調駆動処理部(21・21a)は、画素PIXの応答速度を向上させるために前フィールドから現フィールドへの階調遷移を強調している。これらの結果、上記前フレームと現フレームとの映像データ同

士に殆ど差がない場合であっても、当該画素PIXの表示に不所望な階調遷移が 発生し、当該階調遷移が画像表示装置のユーザにフリッカーとして視認される虞 れがある。

## [0122]

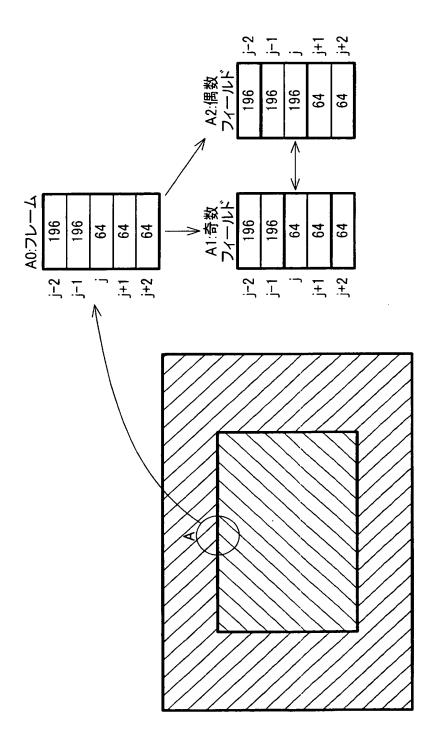

以下では、図8に示すように、ある階調(例えば、196)の背景に、他の階調(例えば、64)の箱が表示されている例を参照して、フリッカーの発生について、さらに詳細に説明する。すなわち、箱の上端付近の領域Aのように、水平ラインに沿ったエッジ付近の領域では、奇数フィールドと偶数フィールドから構成される1フレーム全体でみると、図中、A0に示すように、ある水平ライン(例えば、j行目)を境に、それより上の水平ラインの階調(196)は、196階調、当該水平ライン、および、それより下の水平ラインの階調(64)と異なっている。

#### [0123]

ただし、映像信号DATは、インタレース信号なので、上記1フレームの映像データは、偶数フィールドと奇数フィールドとに分けて伝送されている。ここで、上記j行目が奇数行目とすると、奇数フィールドF(k) では、上記A0に示す各水平ラインのうち、j-2行目、j行目、j+2行目…が伝送され、現&前フィールドの映像信号生成部( $22\cdot22$ a)は、これらの水平ラインの映像データに基づいて、水平ライン間を補間し、図中A1に示すように、j-1行目、j+1行目を生成する。なお、図では、補間によって、基準となる水平ライン(j-2行目など)と同じ階調の水平ライン(j-1行目など)を生成する場合を示している。一方、偶数フィールドF(k+1) では、上記A0に示す各水平ラインのうち、j-1行目、j+1行目…が伝送され、上記映像信号生成部は、図中A2に示すように、これらの水平ライン間の補間によって、j行目、j+2行目を生成する。

#### [0124]

上述したように、j行目は、境界線なので、フレーム単位で見ると、一定の階調(64)であるにも拘わらず、各フィールド間における補間の基準となる水平ラインの変化によって、フィールド単位で見ると、本来の階調(64)と、他の

階調(196)との間の往復応答が発生してしまう。

## [0125]

なお、画素PIXの応答速度が遅く、フィールド毎の往復応答に追従できない場合は、上記往復応答が視認されることがないが、上記各実施形態に係る画像表示装置1は、階調遷移を強調して、画素PIXの応答速度を向上させているので、上記往復応答がフリッカーとして視認される虞れがある。

### [0126]

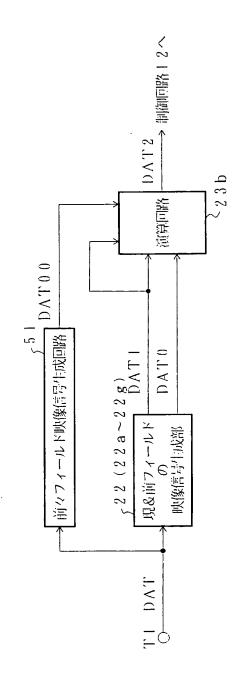

これに対して、本実施形態に係る変調駆動処理部21bは、上記フリッカーの発生を抑制するため、現フレームの映像信号と、映像信号位置が同一の近接するフィールド(本実施形態では、前々フィールド)の映像信号とを比較し、比較結果に応じて、前フィールドから現フィールドへの階調遷移強調の程度を変更している。より詳細には、変調駆動処理部21bは、現フィールドの映像データと、前フレームにおいて、それと同じ画素PIXへの映像データとを比較して、両者が概ね同じであれば、当該画素PIXを駆動する際、前フィールドから現フィールドへの階調遷移を強調する程度(変調の程度)を弱めている。

#### [0127]

すなわち、本実施形態に係る変調駆動処理部21bには、図9に示すように、 上記各実施形態に係る変調駆動処理部21または21aの構成に加え、現フィールド(例えば、偶数フィールド)の映像データを、次のフレームにおいて、当該フィールドに対応するフィールド(偶数フィールド)まで記憶すると共に、これらの記憶した映像データからなる映像信号(本実施形態では、前々フィールドの映像信号)を出力する前々フィールド映像信号生成回路51が設けられている。

## [0128]

さらに、上記変調駆動処理部21bには、演算回路23に代えて、演算回路23bが設けられており、当該演算回路23bは、現フィールドの映像信号と前々フィールドの映像信号とに基づいて、現フィールドの各映像データと、前々フィールドにおいて、それと同じ画素PIXへの映像データとを比較し、ある画素PIXへの映像データ同士が概ね同じであると判定した場合、変調の程度を弱める。また、上記映像データ同士が全く異なると判定した場合、演算回路23bは、

変調の程度を弱めず、前フィールドから現フィールドへの階調遷移を強調する。

## [0129]

なお、本実施形態に係る演算回路23bは、水平ライン間を補間した後の現フィールド映像信号DAT1と、前々フィールドの映像信号とに基づいて、上記両映像データ同士を比較しているので、上記前々フィールド映像信号生成回路51は、映像信号位置が同一の近接するフィールド(前々フィールド)を構成する映像データの水平ライン間を補間し、補間後の映像データを、前々フィールド映像信号DAT00として出力している。

## [0130]

上記構成では、変調駆動処理部21bは、現フィールドの映像データと、前々フィールドにおいて、それと同じ画素PIXへの映像データとを比較し、上記映像データ同士が概ね同じであれば、当該画素PIXを駆動する際、前フィールドから現フィールドへの階調遷移を強調する程度(変調の程度)を弱めている。

## [0131]

したがって、補間後の前フィールド映像信号DATOと現フィールド映像信号DAT1とを比較すると、前フィールドから現フィールドへの階調遷移が発生していても、上記映像データ同士が概ね同じであれば、現フィールドの駆動信号において、当該階調遷移を強調する程度が抑えられる。この結果、映像信号位置が同一の近接するフィールド(前々フィールド)から、現フィールドまでの階調遷移は、通常(階調遷移の強調を弱めない場合)と比べて強調されず、階調遷移の量が抑えられる。

#### $[0\ 1\ 3\ 2\ ]$

これにより、フリッカーの原因となる現象、すなわち、各フィールド毎に異なった水平ラインを基準に補間した結果、フレーム単位では、映像データが変化していないにも拘わらず、フィールド単位でみると、階調が遷移しているという現象が発生しても、階調遷移の量が抑えられるため、フリッカーによる表示品位の低下を抑制できる。

## [0133]

ここで、映像データにノイズがなければ、現フィールドの映像データと、前フ

レームにおいて、それと同じ画素PIXへの映像データとが同一のときに、演算回路23bによる階調遷移強調を停止すればよい。ところが、実際には、映像信号源SOから演算回路23bまでのノイズだけではなく、映像信号源SOが生成する映像信号DAT自体にもノイズが含まれる。したがって、本実施形態に係る変調駆動処理部21bは、上記映像データ同士が概ね同じときに階調遷移を強調する程度(変調の程度)を抑えている。

### [0134]

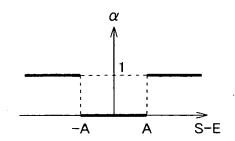

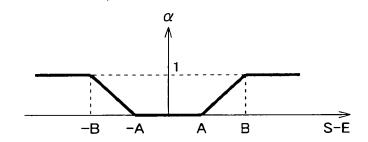

以下では、演算回路23bによる変調の程度変更方法の例について説明する。 第1の変更方法は、図10に示すように、上記両映像データ同士の差 | S-E | が、予め定められた閾値Aを下回っているか否かを判定し、下回っている場合に、現フィールドの映像データをそのまま出力する方法である。

#### [0135]

より詳細には、演算回路 2 3 b が出力する補正映像データ D 2 を、現フィールドの映像データ D + α・補正量 C とする。なお、補正量 C は、現フィールドの映像データと前フィールドの映像データとに応じて予め決定されている。

#### [0136]

通常時、すなわち、上記両映像データ同士の差 |S-E| が上記閾値Aを下回っている場合、演算回路 2.3 b は、現フィールドの映像データD(i,j,k) と前フィールドの映像データD(i,j,k-1) とに基づいて、例えば、LUT (Look Up Ta ble )を参照するなどして、それぞれの組み合わせに応じた補正量Cを求め、さらに、変調の程度  $\alpha=1$  として、上記補正映像データD 2 を算出する。一方、上記両映像データ同士の差 |S-E| が上記閾値Aを下回っている場合、演算回路 2.3 b は、 $\alpha=0$  として、上記補正映像データD 2 を算出する。

#### [0137]

なお、上記では、補正量Cを算出した後、補正映像データD2を算出する場合を例にして説明したが、閾値Aを下回っているか否かに応じて、 $\alpha=0$ としたときの補正映像データD2、または、 $\alpha=1$ としたときの補正映像データD2とを出力できれば、例えば、それぞれを求めるためのLUTを設け、それらを参照して、各補正映像データD2を出力してもよい。

## [0138]

ここで、上記閾値Aとしては、NTSC(National Television System Committee)信号の場合、256階調表示なので、A=8であれば、概ね良好な表示が得られることを確認した。ただし、適切な閾値Aは、映像信号DATの質によって変化するので、映像信号DATの質を判定し、それに応じて閾値Aを変更してもよい。映像信号DATの質の判定基準としては、例えば、映像信号源SOが受像機の場合、電波状況が挙げられる。また、映像信号DATの入力がアナログであるかデジタルであるか、映像信号源SOがビデオ、DVD(Digital Video Disc)あるいはゲーム機であるかなども判定基準として利用できる。なお、ユーザの指示に応じて、演算回路23bが閾値Aを調整してもよいが、上記判定基準に基づいて、映像信号DATの質を判定する回路を画像表示装置1に設け、演算回路23bが判定結果に応じて閾値Aを調整すれば、ユーザの手間を軽減できる。

#### [0139]

ところで、上記第1の変更方法では、回路を簡略化するために、両映像データ同士の差 |S-E| が閾値Aを下回っているか否かによって、変調するか否か( $\alpha=0$  か 1 か)を選択した。これに対して、第2の変更方法は、両映像データ同士の差 |S-E| に応じて、 $\alpha$  が 0 または 1 の 2 値だけではなく、その中間の値も取るように変更する方法である。

### [0140]

例えば、図11の例では、両映像データ同士の差 |S-E| が閾値Aを下回っている場合、 $\alpha=0$ 、閾値Bを上回っている場合は、 $\alpha=1$  に設定し、|S-E| | がAからBまでの間は、値域が $0\sim1$ までの関数 f (|S-E|) によって、 $\alpha$  を設定している。なお、図11では、A=8、B=16であり、 $\alpha=f$  (|S-E|) として、以下のように、

$$|S-E| = 9 \rightarrow \alpha = 1/8$$

;  $|S-E| = 10 \rightarrow \alpha = 2/8$

$|S-E| = 11 \rightarrow \alpha = 3/8$  ;  $|S-E| = 12 \rightarrow \alpha = 4/8$

$|S-E| = 13 \rightarrow \alpha = 5/8$  ;  $|S-E| = 14 \rightarrow \alpha = 6/8$

$|S-E| = 15 \rightarrow \alpha = 7/8$

に設定されている場合を例示している。また、このように設定した演算回路23

bを有する画像表示装置1の画質を評価したところ、第1の変更方法と同様、NTSC信号の場合に、極めて良好な表示品位を得ることができることを確認した。

#### [0141]

なお、上記では、閾値Aが0でない場合を例にして説明したが、第2の変更方法の場合は、閾値Aが0であってもよい。この場合であっても、両映像データ同士の差|S-E|が閾値Bを超えている場合の $\alpha$ よりも、超えていない場合の $\alpha$ の方が小さくなるように設定されていれば、略同様の効果が得られる。

## [0142]

ただし、閾値Aが0か否かに拘わらず、両映像データ同士の差|S-E|が0のときに、 $\alpha=0$ になるように設定されていれば、最も変調の程度を抑制できるので、フリッカーによる表示品位の低下をより確実に抑制できる。このような関数 f (|S-E|) としては、例えば、(S-E) が挙げられる。

#### [0143]

当該構成では、第1の変更方法と異なり、閾値Aと閾値Bとが同じ値ではなく、両映像データ同士の差 |S-E| が閾値Aから閾値Bまでの間は、関数 f (|S-E|) によって、 $\alpha$  を設定している。したがって、第1の変更方法のように、閾値A = 閾値Bの場合と比較して、 $\alpha$  をなだらかに変化させることができる。

## [0144]

この結果、第1の変更方法の場合のように、閾値Aの境界で、 $\alpha$ が0になるか 1になるかが切り換わり、変調の有無による擬似輪郭が発生する場合と異なり、 第2の変更方法では、 $\alpha$ がなだらかに変化しているので、上記擬似輪郭の発生を 抑制でき、特に、人の皮膚のようなグラデーションが存在する映像を表示する場 合であっても、表示品位を高いレベルに維持できる。なお、第2の変更方法であ っても、第1の変更方法と略同様に、映像信号DATの質を判定し、それに応じ て閾値A・Bおよび関数 f(|S-E|)を変更してもよい。

## [0145]

以下では、図12を参照しながら、第2の実施形態の変調駆動処理部21aに 、前々フィールド映像信号生成回路51を追加し、演算回路23を演算回路23 bに入れ換えた場合を例にして、変調駆動処理部 2 1 bの構成例を詳細に説明する。

#### [0146]

すなわち、本構成例では、前々フィールド映像信号生成回路 5 1 が現フィールド (例えば、偶数フィールド) の映像データを映像信号位置が同一の近接するフィールド (偶数フィールド) まで記憶する機能と、現&前フィールドの映像信号生成部 2 2 a が現フィールドの映像データを次のフィールドまで記憶する機能とが、1 つのフィールドメモリによって実現されており、図 7 に示すフィールドメモリ 4 2 に代えて、2 フィールド分の映像データを記憶するフィールドメモリ 4 2 b が設けられている。

#### [0147]

また、調停回路43に代えて、フィールドメモリ42bへ読み書きする調停回路43bが設けられており、当該調停回路43bは、映像信号DATに基づいて、現フィールドF(k)の映像データを、フィールドメモリ42bに記憶できる。さらに、また、調停回路43bは、次のフィールドF(k+1)では、フィールドメモリ42bの記憶領域のうち、前フィールドF(k)の映像データを記憶した記憶領域とは別の記憶領域に、当該フィールドF(k+1)の映像データを記憶できる。さらに、調停回路43bは、前々フィールドF(k-2)の各映像データと、前フィールドF(k-1)の各映像データとをフィールドメモリ42bから読み出して、映像信号DATのドットクロックの2倍の周波数で出力できる。

#### [0148]

一方、前々フィールド映像信号生成回路51には、ラインメモリ52が設けられており、当該ラインメモリ52は、調停回路43bを介して出力されるフィールドメモリ42bの出力信号FMのうち、前々フィールドF(k-2)の各映像データに基づいて、水平ライン間を補間し、補間後の信号を前々フィールド映像信号DAT00として出力できる。なお、図12の例では、フィールドメモリ42bと調停回路43bとラインメモリ52とが図9に示す前々フィールド映像信号生成回路51に対応している。

#### [0149]

また、ラインメモリ44は、第2の実施形態と同様に、フィールドメモリ42 bの出力信号FMのうち、前フィールドF(k-1) の各映像データに基づいて、水平ライン間を補間し、補間後の信号を、前フィールド映像信号DAT0として出力できる。

#### [0150]

ただし、上記各ラインメモリ52・44では、入力信号の周波数と出力信号の周波数とが同一である。また、調停回路43bは、両ラインメモリ52・44の一方に1水平ライン分の映像データを出力した後、他方に1水平ライン分の映像データを出力するので、1水平ライン分の入力信号が入力された後、それと同じ期間の間、入力信号を取得する必要がない。したがって、図13に示すように、1水平ライン分を記憶するFIFO型ラインメモリ52aと、FIFO型ラインメモリのデータを2回出力する制御回路52bとを設けるだけで、各ラインメモリ52・44を構成できる。

## [0151]

一方、演算回路 2 3 b には、演算回路 2 3 と同様に、現フィールド映像信号 D A T 1 および前フィールド映像信号 D A T 0 のうち、互いに同じ画素 P I X (i,j) と対応する映像データ D (i,j,k) および D (i,j,k-1) の対に基づいて、当該映像データ対に対応する補正量 C (i,j,k) を出力する演算処理部 6 1 と、現フィールド映像信号 D A T 1 および前々フィールド映像信号 D A T 0 0 を比較する比較回路 6 2 と、比較回路 6 2 による比較結果と、演算処理部 6 1 が出力する補正量 C (i,j,k) からなる補正映像信号 D A T 2 b と、現フィールド映像信号 D A T 1 とに基づいて、補正映像信号 D A T 2 を生成する変調量調整回路 6 3 とを備えている。

## [0152]

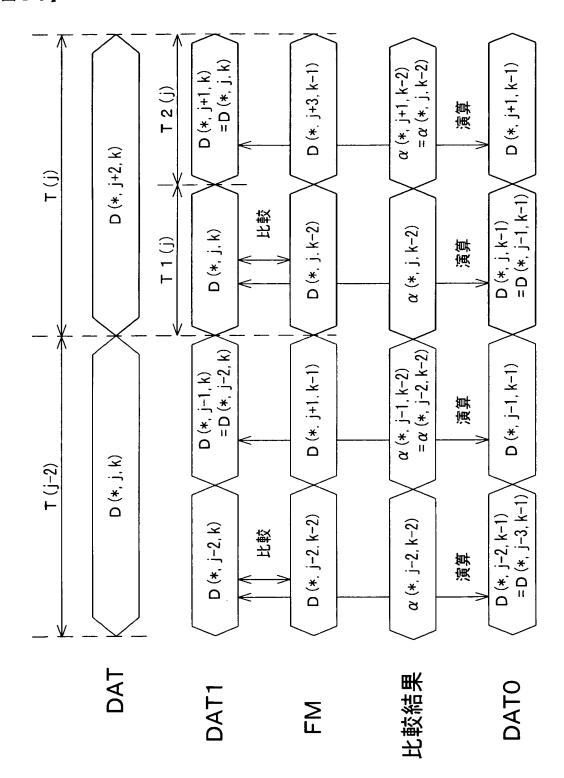

上記構成では、図14に示すように、ラインメモリ41は、図5と同様に、映像信号DATの水平ライン間を補間して、現フィールド映像信号DAT1を出力している。

## [0153]

一方、フィールドメモリ42bは、図5とは異なり、各フィールドF(k) の映

像データが入力されている期間 T(j) の半分の期間 T2(j) において、前フィールド F(k-1) の映像データを記憶した領域から、映像信号 DATのドットクロックの 2 倍の周波数で、前フィールド F(k-1) の各映像データを出力する。

#### [0154]

なお、図14では、ラインメモリ44および52が、それぞれ映像信号DATの1水平ライン分だけ遅れて各映像データを出力する場合を例示している。したがって、調停回路43bは、演算処理部61および比較回路62に到着した時点で、各映像信号DAT1・DAT0・DAT00が同期するように、期間T1(j)に、前々フィールドF(k-2) の映像データD(\*,j+2,k-2) を出力し、期間T2(j)に、前フィールドF(k-1) の映像データD(\*,j+3,k-2) を出力している。

#### [0155]

さらに、ラインメモリ44は、上記フィールドメモリ42bの出力信号FMのうち、上記期間T2に出力された映像データに基づいて、水平ライン間を補間し、前フィールド映像信号DAT0を出力する。上記両フィールド映像信号DAT0・DAT1は、演算処理部61に入力され、各画素PIX(i,j)への補正量C(i,j,k)からなる補正映像信号DAT2bが生成される。

#### [0156]

一方、ラインメモリ52は、上記フィールドメモリ42bの出力信号FMのうち、上記期間T2(j)以外の期間T1(j)に出力された映像データに基づいて、水平ライン間を補間し、前々フィールド映像信号DAT00を出力する。

#### [0157]

さらに、比較回路 62 は、上記両映像信号DAT  $1\cdot$ DAT 00 のうち、互いに同一の画素 PIX(i,j) に対応する映像データD(i,j,k) およびD(i,j,k-2) の対を比較して、変調の程度  $\alpha(i,j,k)$  を決定する。また、変調量調整回路 63 は、ある画素 PIX(i,j) に対応する補正量 C(i,j,k) と、当該画素 PIX(i,j) に対応する変調の程度  $\alpha(i,j,k)$  および現フィールド映像信号DAT 1 の映像データD(i,j,k) とに基づいて、補正映像データD2(i,j,k) を生成する。

## [0158]

例えば、上述した第1の変更方法を採用する構成では、比較回路62は、上記

#### [0159]

これにより、本実施形態に係る変調駆動処理部 2 1 b は、上記映像データ同士が概ね同じときに階調遷移を強調する程度(変調の程度)を抑えることができ、フリッカーの発生を抑制できる。

## [0160]

なお、上記では、演算処理部61へ各画素PIX(i,j) 毎の変調の程度  $\alpha$ (i,j,k) を通知するために、水平ライン間を補間するラインメモリ52を比較回路62の前段に設け、比較回路62が、各画素PIX(i,j) 毎に、前々フィールド映像信号DAT00と現フィールド映像信号DAT1とを比較して、変調の程度  $\alpha$ (i,j,k) を出力する構成について説明したが、図15に示すように、水平ライン間を補間するラインメモリを、比較回路62の後段に設けてもよい。

### [0161]

図15に示す構成例は、第1の実施形態の変調駆動処理部21に、前々フィールド映像信号生成回路51を追加し、演算回路23を演算回路23bに入れ換えた構成である。

## [0162]

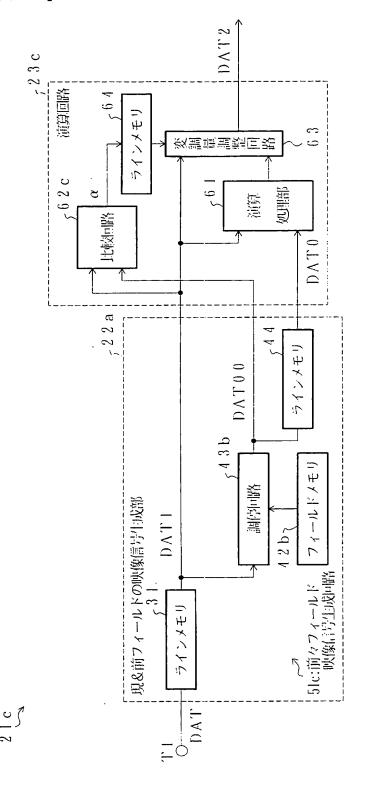

本構成例に係る変調駆動処理部21cでも、図12に示す変調駆動処理部21bと同様に、前々フィールド映像信号生成回路51と現&前フィールドの映像信号生成部22との間で、フィールドメモリ42bが共用されており、ラインメモリ44は、フィールドメモリ42bが期間T2(j)に出力した映像データに基づいて、水平ライン間を補間し、前フィールド映像信号DAT0を生成している。

#### [0163]

また、本構成例に係る変調駆動処理部 2 1 c の演算回路 2 3 c は、図 1 2 c に示す変調駆動処理部 2 1 b と略同様の演算処理部 6 1、比較回路 6 2 c および変調量調整回路 6 3 c 備えている。ただし、本構成例では、図 1 2 c に示すラインメモリ 5 2 が省略されており、比較回路 6 2 c に代えて設けられた比較回路 6 2 c は、図 1 6 c に示すように、期間 1 (j) に現る前フィールドの映像信号生成部 2 2 a から出力された現フィールド 1 (j) に現る前フィールドの映像信号生成部 1 (j) と、当該期間 1 (j) に、フィールドメモリ 1 (j) に、フィールドメモリ 1 (j) に、フィールドド 1 (k) の映像データであって、上記現フィールド 1 (k) の各映像データと同じ画素 1 (k) の映像データであって、上記現フィールド 1 (k) の各映像データと同じ画素 1 (k) の 1

#### [0 1 6 4]

さらに、演算回路23cには、ラインメモリ52と略同様のラインメモリ64が設けられており、比較回路62cの出力信号に基づいて、水平ライン間を補間し、演算回路23bへ比較結果を供給する。なお、ラインメモリ64のビット数は、ラインメモリ52とは異なり、映像データの記憶に必要なビット数ではなく、比較結果の記憶に十分なビット数に設定されている。

#### [0165]

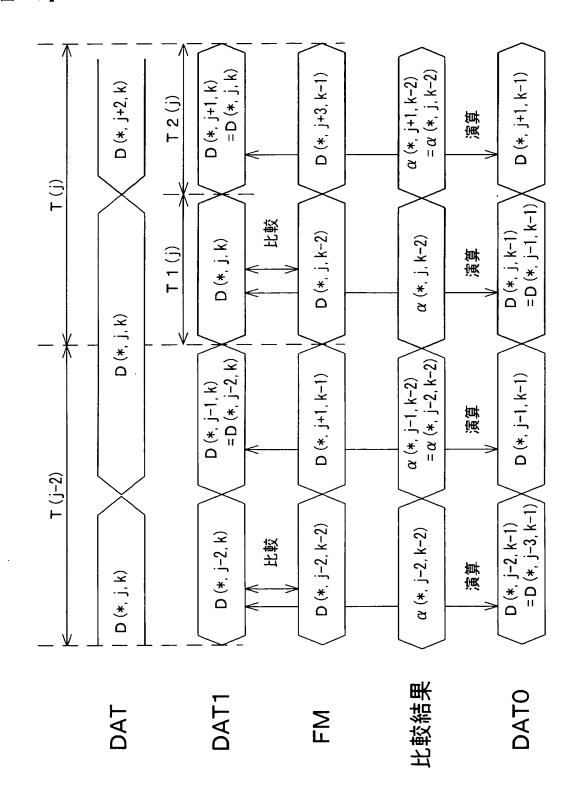

ここで、調停回路43bは、図15に示すように、期間T2(j)中、前フィールドF(k-1)の映像データ(例えば、D(\*,j+3,k-1))を出力しており、前々フィールドF(k-2)の映像データを出力していないので、比較回路62cは、前々フィールド映像信号DAT1とを比較できない。

#### [0166]

ところが、前々フィールド映像信号DAT00と現フィールド映像信号DAT1とは、フレームは異なっているが、互いに同じフィールドの映像信号である。したがって、上記期間T1(j) に印加された両映像データを比較することによって得られた1水平ライン分の比較結果 $\alpha$ (\*,j,k) は、次の水平ライン分の比較結果 $\alpha$ (\*,j+l,k) と同じである。この結果、ラインメモリ64が、ラインメモリ52と同様に、1水平ライン分の比較結果を記憶し、当該1水平ライン分の比較結

果を 2 回出力することによって、演算回路 2 3 c は、正しい補正映像信号 DAT 2 を出力できる。

## [0167]

ところで、上記では、図6に示すように、ラインメモリ31(41)が2つの FIFO型メモリ31a・31bを備え、映像信号DATの1水平ライン分だけ 遅れて、映像データを出力する場合を例にして説明したが、これに限るものでは ない。

#### [0168]

例えば、図13に示すラインメモリ52(44)と同様に、1水平ライン分の映像データを記憶するFIFO型メモリ71と、映像信号DATのドットクロックの2倍の周波数で、FIFO型メモリ71に蓄積された映像データのうちの1つを選択し、出力する制御回路72とを備えていてもよい。

#### [0169]

この場合、図17に示すように、FIFO型メモリ71が1水平ライン分の映像データD(\*,j,k) の出力を1回目に開始する時点では、映像信号DATの方が、映像信号DATの1/2水平ライン分だけ、現フィールド映像信号DAT1よりも先行している。ここで、上記位相差は、ラインメモリ31cが映像データを出力する度に、ドットクロックの周期の1/2ずつ無くなっていく。ところが、上述したように、1回目の開始時点で、1/2水平ライン分だけ、映像信号DAT0が先行しているので、FIFO型メモリ71は、何ら支障なく、1水平ライン分の映像データD(\*,j,k)0を蓄積しながら、1水平ライン分の映像データD(\*,j,k)1を書積しながら、1水平ライン分の映像データD(\*,j,k)2を書積しながら、1水平ライン分の映像データD(\*,j,k)3を出力できる。

#### [0170]

ここで、FIFO型メモリ71へ1水平ライン分の映像データD(\*,j,k)が入力された後、次の水平ラインの映像データD(\*,j+l,k)がFIFO型メモリ71へ順次入力されていく。ところが、FIFO型メモリ71の出力のドットクロックの方が映像信号DATのドットクロックよりも高い。したがって、例えば、FIFO型メモリ71の記憶容量を、1水平ラインよりも1映像データ分大きく設定するなどして、最初の映像データD(1,j,k)が上書きされるよりも前に、2回

目の最初の映像データD(1,j,k) を出力できれば、FIFO型メモリ71は、各映像データD(\*,j,k) の記憶領域が上書きされるよりも前に、2回目の各映像データD(\*,j,k) を出力できる。

#### [0171]

#### [第4の実施形態]

ところで、上記第3の実施形態では、現フィールドの映像データと、映像信号位置が同一の近接するフィールドにおいて、それと同じ画素PIXへの映像データとを比較して、両者が概ね同じであれば、当該画素PIXを駆動する際、前フィールドから現フィールドへの階調遷移を強調する程度(変調の程度)を弱める構成によって、フレーム単位では、映像データが殆ど変化していない場合の階調遷移の量を抑え、フリッカーによる表示品位の低下を抑制できる。

#### [0172]

これに対して、本実施形態に係る変調駆動処理部 2 1 d (図 1 または図 7 参照) では、他の構成によって、フリッカーが発生した場合に発生する現象のうち、表示品位を特に低下させる現象の発生を抑制している。

#### [0173]

具体的には、画素 PIX(i,j) の応答速度が最速になるように、演算回路(23~23c)が、前フィールドから現フィールドへの階調遷移を強調した場合、往復応答が発生したときに、往路の応答速度と復路の応答速度とのうちの一方が他方よりも速くなることが多い。

#### [0174]

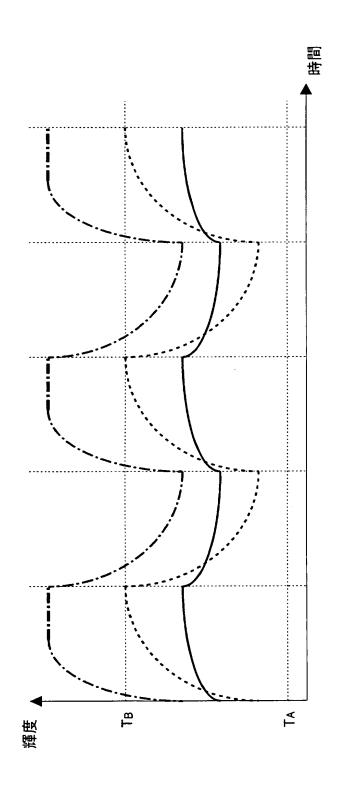

例えば、図18に示すように、階調レベル(輝度)TAからTBへの階調遷移の方が、階調レベルTBからTAへの階調遷移よりも速くなった場合、往復応答が発生すると、階調レベルの平均値は、階調レベルTAとTBとの間の中間値よりも大きくなってしまう。特に、上記両階調遷移の速度差が大きくなると、階調レベルの平均値が、高い方の階調レベルTAを超える現象が発生する。

#### [0175]

この現象が発生した場合、その画素 PIXの階調レベルは、上記各階調レベル TAおよびTBのいずれよりも大きいので、ユーザの目につきやすく、画像表示 装置の表示品位を大きく低下させてしまう。例えば、図8と同様に、階調レベル TAの背景に階調レベルTBの箱を表示しているとき、両者のエッジ領域Aの画素 PIXが、背景および箱のいずれよりも高い階調レベルになるので、光って見えてしまう。

#### [0176]

本実施形態に係る変調駆動処理部21dは、上記現象の発生を防止するために、往復応答の往路および復路のうち、より速く階調遷移する方において、階調遷移を強調する程度を抑制し、より遅く階調遷移する方の速度に近づけている。

## [0177]

また、上記階調遷移強調を抑制する程度は、画素PIXが、ある輝度TAおよびTBの間で往復駆動された場合に、当該画素PIXの時間的積分輝度が、上記輝度TAからTBまでの範囲に入るように設定されている。

## [0178]

上記構成では、変調駆動処理部21dは、画素PIXが、ある輝度TAおよびTBの間で往復駆動された場合に当該画素PIXの時間的積分輝度が上記輝度TAからTBまでの範囲に入る程度に、前フィールドから現フィールドへの階調遷移を強調している。

#### [0179]

## [0180]

この結果、当該画素PIX(i,j)の輝度が、自分自身への映像データD(i,j,k))、および、近隣の映像データD(i,j,k) よりも、明るくなったり、暗くなったりする現象を回避できる。これにより、画像表示装置の表示品位低下を抑制できる。

## [0181]

また、上記構成では、演算回路 23 が両フィールド映像信号  $DAT0 \cdot DAT1$ 、それぞれの映像データ D(i,j,k-1) および D(i,j,k) を参照して、補正映像データ D2(i,j,k) を導出しており、上記階調遷移強調の程度は、補正映像データ D2(i,j,k) を導出する時の計算方法、あるいは、導出時に参照するデータを設定することによって設定されている。

## [0182]

したがって、第3の実施形態と異なり、第1および第2の実施形態の構成に、 フリッカーに起因する表示品位低下を抑制するための部材を特に追加することな く、当該表示品位低下を抑制できる。

## [0183]

さらに、本実施形態では、上記階調遷移強調の程度は、全ての階調間の応答速度が概ね一致するように設定されている。より詳細には、各階調遷移のうち、最も強調しても一番遅い階調遷移の応答速度に、他の階調遷移の応答速度が略一致するように、他の階調遷移強調の程度が抑えて設定されている。

## [0184]

当該構成では、全ての階調間の応答速度が概ね等しくなるので、各階調間の応答速度がバラバラの場合に発生する不具合、すなわち、動いている物体を表示している際に、高速に応答する画素と低速に応答する画素とが混在すると、上記物体が透けて見えるという不具合の発生を防止でき、表示品位低下を抑制できる。

#### [0185]

#### [第5の実施形態]

上記第1ないし第4の実施形態では、現フィールドの各映像データの水平ライン間を補間して、現フィールド映像信号DAT1を生成する際、および、前フィールドの各映像データの水平ライン間を補間して、前フィールド映像信号DAT0を生成する際、ある水平ラインの映像データD(\*,j,k)と同じ映像データを次の水平ラインの映像データD(\*,j+l,k)として出力することによって補間する場合を例にして説明した。

#### [0186]

これに対して、本実施形態では、他の補間方法によって、現フィールドの映像

データおよび前フィールドの映像データを補間する構成について説明する。なお、当該構成は、上述の各構成の変調駆動処理部(21~21d)に適用できるが、以下では、一例として、図9に適用した場合を例にして説明する。

## [0187]

すなわち、本実施形態に係る変調駆動処理部 21eでは、現&前フィールドの映像信号生成部( $22\sim22a$ )に代えて、現および前フィールドを構成する 200の行の映像信号を平均した映像信号によって補間する映像信号生成部 22eが設けられている。

### [0188]

上記映像信号生成部 2 2 e は、前フィールド F (k-1) の水平ライン L (j-2) および L (j) 間を補間して、水平ライン L (j-1) の映像データ D (\*,j-1,k-1) を生成する際、映像データ D (i,j-2,k-1) と、映像データ D (i,j,k-1) とを平均して、映像データ D (i,j-1,k-1) を生成する。

#### [0189]

同様に、現フィールドF(k) の水平ラインL(j-2) およびL(j) 間を補間して、水平ラインL(j-1) の映像データD(\*,j-1,k) を生成する際、映像データD(i,j,k) は、映像データD(i,j,k) と、映像データD(i,j,k) とを平均することによって生成される。

### [0190]

当該構成では、各フィールドにおいて、直前の水平ラインと現在の水平ラインとを平均することで、両者の間の水平ラインを生成する。したがって、同一内容の映像データによって、水平ライン間を補間する場合よりも、滑らかな映像を表示できる。さらに、他の映像信号を参照する場合、あるいは、上記2つの水平ラインに基づく場合であっても、平均以外の演算を用いて生成する場合と比較して、簡単な回路構成で補間できる。この結果、比較的簡単な回路構成で、より表示品質の良い画像表示装置1を実現できる。

## [0191]

また、上記現&前フィールドの映像信号生成部22eに代えて、現フィールドの映像データに基づいて、現フィールドをインタレースープログレッシブ変換す

ると共に、前フィールドの映像データに基づいて、前フィールドをインタレース ープログレッシブ変換することによって、現および前フィールド映像信号DAT 1・DAT0を生成する映像信号生成部22fを設けてもよい。

#### [0192]

上記映像信号生成部  $2\ 2\ f$  は、前フィールドF(k-1) の水平ラインL(j-2) およびL(j) 間を補間して、水平ラインL(j-1) の映像データD(\*,j-1,k-1) を生成する際、水平ラインL(j-1) を構成する映像データのうちの複数と、水平ラインL(j) を構成する映像データのうちの複数とに基づいて、ある画素PIX(i,j-1) への映像データD(i,j,k-1) を生成する。

## [0193]

同様に、現フィールドF(k) の水平ラインL(j-2) およびL(j) 間を補間して、水平ラインL(j-1) の映像データD(\*,j-1,k) を生成する際、ある画素PIX (i,j-1) への映像データD(i,j,k) は、水平ラインL(j-1) を構成する映像データのうちの複数と、水平ラインL(j) を構成する映像データのうちの複数とに基づいて生成される。

#### [0 1 9 4]

当該構成では、フィールドを構成する2つの水平ラインのうちの一方を構成する複数の画素への映像データと、他方を構成する複数の画素への映像データとに基づいて、補間する水平ラインの1画素への映像信号が生成される。このように、前後水平ラインの左右複数画素も補間演算の対象となり、例えば、表示に斜め線があるか否かなどの判定に基づく補間が可能になる。したがって、同一内容の映像データによって補間する場合や平均によって補間する場合よりも滑らかに、前および現フィールドの各水平ライン間を補間できる。この結果、より表示品質の良い画像表示装置1を実現できる。

#### [0195]

さらに、上記現&前フィールドの映像信号生成部22fに代えて、現フィールドの前後のフィールドの映像データに基づいて、現フィールドをインタレースープログレッシブ変換すると共に、前フィールドの前後のフィールドの映像データに基づいて、前フィールドをインタレースープログレッシブ変換することによっ

て、現および前フィールド映像信号DAT1・DAT0を生成する映像信号生成部22gを設けてもよい。

## [0196]

当該構成では、複数フィールドの映像データを参照して、前および現フィールドの映像データの水平ライン間が補間される。したがって、より滑らかに前および現フィールドの各水平ライン間を補間できる。この結果、より表示品質の良い画像表示装置1を実現できる。また、複数フィールドの映像データを補間演算の対象とするので、静止画か否かを判定でき、静止画であれば、補間すべき映像データとして、前フィールドと同じ映像データを用いることができる。この場合は、フリッカーの発生を抑えることができる。

## [0197]

なお、上記各実施形態では、各フィールドにおいて、映像データが水平ライン毎に時分割伝送される場合を例にして説明したが、ライン毎に伝送されれば、略同様の効果が得られる。また、上記各実施形態では、垂直配向モードかつノーマリブラックモードの液晶セルを表示素子として用いた場合を例にして説明したが、これに限るものではない。応答速度を向上するために、階調遷移を強調するように変調して駆動することが望まれると共に、輝度を向上するために、フィールド毎に全画素PIXを駆動することが望まれる表示素子であれば、略同様の効果が得られる。

## [0198]

ただし、液晶セルは、CRTに比べて応答速度が遅く、遷移階調によって、通常のフレーム周波数(60Hz)に対応した書き換え時間(16.7msec)で応答が完了しないこともあるため、前回から今回への階調遷移を強調するように、駆動信号を変調することが望まれる。また、液晶セルでは、暗表示時にも光源が電力を消費しているので、フィールド毎に全画素PIXを駆動することによって、消費電力を増大させずに輝度を向上できる。したがって、表示素子として、液晶セルを採用すると、特に効果が大きい。

## [0199]

また、上記各実施形態では、変調駆動処理部を構成する各部材がハードウェア

のみで実現されている場合を例にして説明したが、これに限るものではない。各部材の全部または一部を、上述した機能を実現するためのプログラムと、そのプログラムを実行するハードウェア(コンピュータ)との組み合わせで実現してもよい。一例として、画像表示装置1に接続されたコンピュータが、画像表示装置1を駆動する際に使用されるデバイスドライバとして、変調駆動処理部(21~21e)を実現してもよい。また、画像表示装置1に内蔵あるいは外付けされる変換基板として、変調駆動処理部が実現され、ファームウェアなどのプログラムの書き換えによって、当該変調駆動処理部を実現する回路の動作を変更できる場合には、当該ソフトウェアを配布して、当該回路の動作を変更することによって、当該回路を、上記各実施形態の変調駆動処理部として動作させてもよい。

## [0200]

これらの場合は、上述した機能を実行可能なハードウェアが用意されていれば、当該ハードウェアに、上記プログラムを実行させるだけで、上記各実施形態に係る変調駆動処理部を実現できる。

## [0201]

## 【発明の効果】

本発明に係る表示装置の駆動方法は、以上のように、変調工程の前に実施され、前フィールドの映像信号を補間して、1フレーム分の映像信号を生成する前フィールド補間工程と、上記変調工程の前に実施され、現フィールドの映像信号を補間して、1フレーム分の映像信号を生成する現フィールド補間工程とを含み、上記変調工程では、各画素の駆動信号を変調する際、前フィールドの映像信号のうち、当該画素への駆動信号を生成するための映像信号を参照して、当該画素の駆動信号を変調する構成である。また、本発明に係るプログラムは、以上のように、上述の各工程をコンピュータに実行させるプログラムであり、当該プログラムがコンピューで実行されると、当該コンピュータは、表示装置を上記駆動方法で駆動できる。

## [0202]

これらの構成では、変調工程の前に、前フィールドの映像信号および前フィールドの映像信号を補間して、それぞれ1フレーム分の映像信号が生成されており

、変調工程では、前フィールドの映像信号のうち、当該画素への駆動信号を生成するための映像信号を参照して、当該画素の駆動信号を変調する。

#### [0203]

したがって、各フィールド毎に1フレーム分の絵素群が駆動されることによって輝度を増大し、前フィールドの映像信号を参照して駆動信号を変調することによって、画素の応答速度を向上できるにも拘わらず、比較対象のズレに起因する誤変調が発生しない。この結果、表示品質の良い表示装置を実現できるという効果を奏する。

## [0204]

さらに、上記構成では、前フィールドの映像信号を参照して変調しているので、変調によって画素の応答速度を向上できるにも拘わらず、前フレームの映像信号を参照して変調する場合よりも、変調に必要な記憶容量を削減できるという効果を併せて奏する。

#### [0205]

本発明に係る表示装置の駆動方法は、以上のように、上記構成に加えて、上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する行の映像信号と同一内容の映像信号によって補間する構成である。

### [0206]

当該構成では、補間対象のフィールドを構成する行の映像信号と同一内容の映像信号によって、他のフィールドのうち、当該行に連続する行を補間している。 したがって、1行分の映像信号を記憶し、当該行分の映像信号を複数回出力する だけで、行間を補間でき、回路構成を簡略化できるという効果を奏する。

## [0207]

本発明に係る表示装置の駆動方法は、以上のように、同一内容の映像信号で補間する代わりに、上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する2つの行の映像信号を平均した映像信号によって補間する構成である。

## [0208]

当該構成では、補間対象のフィールドの前の行と現在の行とを平均することで、両者の間の行を生成する。したがって、同一内容の映像信号で補間する場合よりも滑らかな映像を表示できる。さらに、他の映像信号を参照する場合、あるいは、上記2つの行に基づく場合であっても、平均以外の演算を用いて生成する場合と比較して、簡単な回路構成で補間できる。この結果、比較的簡単な回路構成で、より表示品質の良い表示装置を実現できるという効果を奏する。

## [0209]

本発明に係る表示装置の駆動方法は、以上のように、上記構成に加えて、上記両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を補間する際、補間する行に連続する行であって、しかも、補間対象のフィールドを構成する2つの行の映像信号に基づいて、補間する行の映像信号を生成すると共に、上記2つの行の一方を構成する複数の画素への映像信号と、他方を構成する複数の画素への映像信号とに基づいて、補間する行の1つの画素への映像信号を生成する構成である。

## [0210]

当該構成では、補間対象のフィールドの2行のうちの一方を構成する複数の画素への映像信号と、他方を構成する複数の画素への映像信号とに基づいて、補間する行の1画素への映像信号が生成されるので、同一内容の映像信号によって補間する場合や平均によって補間する場合よりも滑らかに補間対象のフィールドの各行間を補間できる。この結果、より表示品質の良い表示装置を実現できるという効果を奏する。

## [0211]

本発明に係る表示装置の駆動方法は、以上のように、上記構成に加えて、上記 両補間工程の少なくとも1つでは、他のフィールドを構成する各行の映像信号を 補間する際、当該行に連続する行であって、しかも、補間対象のフィールドを構成する2つの行の映像信号と補間対象に隣接するフィールドの映像信号とに基づいて補間する構成である。

## [0212]

当該構成では、補間対象のフィールドの映像信号だけではなく、補間対象に隣接するフィールドの映像信号も参照して、補間対象のフィールドの各行間が補間されるため、より滑らかに補間対象のフィールドの各行間を補間できる。この結果、より表示品質の良い表示装置を実現できるという効果を奏する。

## [0213]

本発明に係る表示装置の駆動方法は、上記構成に加えて、1フレームは、2フィールドから構成されており、2フィールド前の映像信号と、現フィールドの映像信号との比較結果を参照して、上記変調工程における変調の程度を調整する調整工程を含んでいる構成である。

#### [0214]

当該構成では、2フィールド前の映像信号と現フィールドの映像信号との比較結果を参照して、上記変調工程における変調の程度を調整している。したがって、比較結果に応じて上記変調工程における変調の程度を調整することによって、画素の往復駆動時の階調遷移量を抑制できる。この結果、フリッカーの発生を防止でき、表示装置の表示品質を向上できるという効果を奏する。

## [0215]

本発明に係る表示装置の駆動方法は、以上のように、上記構成に加えて、上記調整工程では、2フィールド前の映像信号と現フィールドの映像信号とが概ね同じであれば、上記変調工程における変調を阻止する構成である。

## [0216]

当該構成では、上記両映像信号が概ね同じであれば、変調が阻止されるので、 往復駆動が発生しても、階調遷移量が最小限に保たれる。この結果、フリッカー の発生を防止でき、表示装置の表示品質を向上できるという効果を奏する。

#### [0217]

本発明に係る表示装置の駆動方法は、以上のように、上記構成に加えて、上記調整工程では、2フィールド前の映像信号と現フィールドの映像信号との差が予め定められた範囲であれば、両者の差に応じて、変調を抑制する程度を、変調を抑制しないレベルから、変調を阻止するレベルにまで徐々に変化させる構成である。

## [0218]

当該構成では、2フィールド前の映像信号と現フィールドの映像信号との差が 予め定められた範囲であれば、変調を抑制する程度が両映像信号の差に応じて徐 々に変化する。したがって、変調抑制の程度の変化が映像に顕れてしまい、表示 品位を低下させてしまうという現象の発生を防止できるという効果を奏する。

#### [0219]

本発明に係る表示装置の駆動方法は、以上のように、上記構成に加えて、上記変調工程では、前フィールドから現フィールドへの階調遷移を強調するように、上記画素群の駆動信号が変調されており、さらに、上記変調工程における階調遷移強調の程度は、第1の階調から第2の階調への階調遷移を最も強調したときの応答速度と、第2の階調から第1の階調への階調遷移を最も強調したときの応答速度とのうちの速い方を、遅い方に近づけることによって、ある画素の前フィールドから現フィールドへの階調遷移が、上記第1の階調から第2の階調への階調遷移と第2の階調から第1の階調への階調遷移とを繰り返すときに、当該画素の時間的積分輝度が上記第1の階調から第2の階調までの間の値になるように設定されている構成である。

## [0220]

当該構成では、変調工程における階調遷移強調の程度が上記のように設定されているので、各フィールド毎に1フレーム分の絵素群が駆動されることによって輝度を増大し、前フィールドの映像信号を参照して駆動信号を変調することによって画素の応答速度を向上できるにも拘わらず、往復駆動された画素が周囲から浮いて見えるという現象の発生を防止でき、表示装置の表示品質を向上できるという効果を奏する。

#### [0221]

本発明に係る表示装置の駆動方法は、以上のように、上記構成に加えて、上記 変調工程では、上記変調工程における階調遷移強調の程度が、各階調遷移のうち 、最も強調しても一番遅い階調遷移の応答速度に、他の階調遷移の応答速度が略 一致するように、他の階調遷移強調の程度が抑えて設定されている構成である。

#### [0222]

当該構成では、全ての階調間の応答速度が概ね等しくなるので、各階調間の応答速度がバラバラの場合に発生する不具合、すなわち、動いている物体を表示している際に、高速に応答する画素と低速に応答する画素とが混在すると、上記物体が透けて見えるという不具合の発生を防止できるという効果を奏する。

#### [0223]

本発明に係る表示装置の駆動装置は、以上のように、現および前フィールドの映像信号生成手段は、前フィールドを構成する各行の間を補間して、上記前フィールド映像信号として、1フレーム分の前フィールド映像信号を生成する前フィールド補間手段と、現フィールドを構成する各行の間を補間して、上記現フィールド映像信号として、1フレーム分の現フィールド映像信号を生成する現フィールド補間手段とを備え、駆動信号生成手段は、上記各画素の駆動信号を生成する際、上記前フィールド映像信号のうち、当該画素への駆動信号を生成するための映像信号を参照して、当該画素の駆動信号を変調する構成である。

## [0224]

上記構成では、両フィールド補間手段の出力に基づいて、駆動信号生成手段が 駆動信号を生成するので、当該表示装置の駆動装置は、上述の表示装置の駆動方 法で表示装置の画素群を駆動できる。したがって、上記表示装置の駆動方法と同 様、各フィールド毎に1フレーム分の絵素群が駆動されることによって輝度を増 大し、前フィールドの映像信号を参照して駆動信号を変調することによって画素 の応答速度を向上できるにも拘わらず、比較対象のズレに起因する誤変調が発生 せず、表示品質の良い表示装置を実現できるという効果を奏する。

#### [0225]

さらに、上記構成では、前フィールドの映像信号を参照して変調しているので、変調によって画素の応答速度を向上できるにも拘わらず、前フレームの映像信号を参照して変調する場合よりも、変調に必要な記憶容量を削減できるという効果を併せて奏する。

## [0226]

本発明に係る表示装置の駆動装置は、以上のように、上記構成に加えて、上記 インタレース信号では、2フィールドの映像から1フレームの映像が構成されて おり、上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を 1 行分記憶し、1 行分の映像信号を、上記インタレース信号のドットクロックの 2 倍の周波数で 2 回出力するラインメモリを備え、上記前フィールド補間手段は、現フィールドを構成する各行の映像信号を格納し、次のフィールドまで記憶するフィールドメモリと、上記ラインメモリの出力に基づいて、現フィールドを構成する各行の映像信号を上記フィールドメモリに格納すると共に、前のフィールドを構成する各行の映像信号を、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波数で 2 回出力させる制御手段とを備えている構成である

## [0227]

当該構成では、前フィールドの映像データを出力するために必要なフィールドメモリが、前フィールド補間手段としても動作しており、当該フィールドメモリが、前フィールド映像信号として、前フィールドの1行分の映像データを2回出力している。したがって、前フィールド補間手段とフィールドメモリとを別に設けた構成、例えば、フィールドメモリがインタレース信号と同じ周波数で映像信号を出力し、フィールドメモリの後段に設けられたラインメモリが、フィールドメモリの出力を1行分記憶して、1水平ライン分の映像データを2回出力する構成と比較して、ラインメモリの数を削減できる。この結果、小さな回路規模で、表示装置の駆動装置を実現できるという効果を奏する。

## [0228]

本発明に係る表示装置の駆動装置は、以上のように、上記現および前フィールドの映像信号生成手段は、上記インタレース信号を1フィールド分遅らせて出力するフィールドメモリを備え、上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行分記憶すると共に、当該1行分の映像信号を、上記インタレース信号のドットクロックの2倍の周波数で2回出力する現フィールドラインメモリを備え、上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリと同じ周波数で2回出力する前フィールドラインメモリを備えている構成である。

## [0229]

当該構成では、フィールドメモリが前フィールド補間手段として動作する構成と比較して、フィールドメモリが出力する映像信号のドットクロックの周波数は、インタレース信号のドットクロックの周波数に抑えられている。したがって、フィールドメモリの動作周波数を抑制できる。この結果、比較的回路設計が容易で、EMI対策しやすい表示装置の駆動装置を実現できるという効果を奏する。

### [0230]

本発明に係る表示装置の駆動装置は、以上のように、上記各構成に加えて、現フィールドの映像信号を、現フィールドと映像信号の位置が同一の近接するフィールドまで記憶し、同一位置フィールド映像信号として出力する同一位置フィールド映像信号生成手段を備え、上記駆動信号生成手段は、上記同一位置フィールド映像信号と現フィールド映像信号とを比較し、比較結果に応じて、前フィールドから現フィールドへの階調遷移強調の程度を変更して、駆動信号を生成する構成である。

## [0231]

当該構成では、上記駆動信号生成手段が同一位置フィールド映像信号と現フィールド映像とを比較し、比較結果に応じて、前フィールドから現フィールドへの 階調遷移強調の程度を変更している。したがって、上述の表示装置の駆動方法の うち、比較結果に応じて階調遷移強調の程度を調整する駆動方法と同様に、比較 結果に応じて画素の往復駆動時の階調遷移量を抑制できる。この結果、フリッカーの発生を防止でき、表示装置の表示品質を向上できるという効果を奏する。

#### [0232]

本発明に係る表示装置の駆動装置は、以上のように、上記構成に加えて、上記インタレース信号では、2フィールドの映像から1フレームの映像が構成されており、上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行分記憶し、1行分の映像信号を、上記インタレース信号のドットクロックの2倍の周波数で2回出力する現フィールドラインメモリを備え、さらに、現フィールドの映像信号を2つ後のフィールドまで記憶するフィールドメモリと、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波数で、前フィ

ールドの1行分の映像信号と前々フィールドの1行分の映像信号とを交互に出力させる制御手段と、上記フィールドメモリが出力する前々フィールドの映像信号を1行分記憶すると共に、上記前々フィールド映像信号として、上記現フィールドラインメモリと同じ周波数で当該1行分の映像信号を2回出力する前々フィールドラインメモリとが設けられ、上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリと同じ周波数で2回出力する前フィールドラインメモリを備え、上記駆動信号生成手段は、上記現フィールド補間手段が出力する現フィールド映像信号と上記前々フィールド映像信号とを上記各画素毎に比較して、上記各画素毎に、比較結果を出力する比較手段と、比較結果に基づいて、各画素の駆動信号の変調の程度を調整する調整手段とを備えている構成である。

#### [0233]

当該構成では、前々フィールド映像信号生成手段のフィールドメモリが、前フィールドの映像信号と前々フィールドの映像信号とを交互に出力し、現および前フィールドの映像信号生成手段の前フィールド補間手段が、当該フィールドメモリの出力に基づいて前フィールド映像信号を生成している。

## [0234]

したがって、上記フィールドメモリとは別に、前フィールドの映像信号を記憶 するフィールドメモリを設け前フィールド映像信号を生成する構成よりも少ない 記憶容量で表示装置の駆動装置を実現できるという効果を奏する。

#### [0235]

本発明に係る表示装置の駆動装置は、以上のように、上記インタレース信号が2フィールドの映像から1フレームの映像が構成されている場合に、フィールドメモリの出力する前々フィールドの映像信号を補間する代わりに、上記現フィールド補間手段は、現フィールドを構成する各行の映像信号を1行分記憶し、1行分の映像信号を、上記インタレース信号のドットクロックの2倍の周波数で2回出力する現フィールドラインメモリを備え、さらに、現フィールドの映像信号を2つ後のフィールドまで記憶するフィールドメモリと、当該フィールドメモリから、上記現フィールドラインメモリと同じ周波数で、前フィールドの1行分の映

63/

像信号と前々フィールドの1行分の映像信号とを交互に出力させる制御手段とが設けられ、上記前フィールド補間手段は、上記フィールドメモリが出力する映像信号を1行分記憶すると共に、当該1行分の映像信号を、上記現フィールドラインメモリと同じ周波数で2回出力する前フィールドラインメモリを備え、上記駆動信号生成手段は、上記現フィールド補間手段が出力するフィールド映像信号を構成する各行の映像信号のうち、1行おきの映像信号と、上記前々フィールド映像信号とを上記各画素毎に比較して、上記各画素毎に、比較結果を出力する比較手段と、比較結果を1行分記憶すると共に、1行分の比較結果を、上記現フィールドラインメモリと同じ周波数で2回出力する比較結果ラインメモリと、当該比較結果ラインが出力する各画素の比較結果に応じて、当該画素の駆動信号の変調の程度を調整する調整手段とを備えている構成である。

#### [0236]

当該構成では、フィールドメモリの出力する前々フィールドの映像信号の行間を前々フィールドラインメモリが補間する代わりに、比較結果ラインメモリが、比較結果の行間を補間している。ここで、多くの場合、比較結果の記憶に必要な記憶容量は、映像データ自体の記憶に必要な記憶容量よりも少ない。したがって、前々フィールドの映像信号自体ではなく、比較結果の行間を補間することによって、表示装置の駆動装置に必要な記憶容量を削減でき、回路規模を縮小できるという効果を奏する。

## 【図面の簡単な説明】

#### 【図1】

本発明の実施形態を示すものであり、画像表示装置の変調駆動処理部の要部構成を示すブロック図である。

#### 【図2】

上記画像表示装置の要部構成を示すブロック図である。

#### 【図3】

上記画像表示装置に設けられた画素の構成例を示す回路図である。

#### 【図4】

上記画像表示装置の動作を示すフローチャートである。

## 【図5】

上記画像表示装置の動作を示すタイミングチャートである。

## 【図6】

上記変調駆動処理部に設けられたラインメモリの構成例を示すブロック図である。

## 【図7】

本発明の他の実施形態を示すものであり、変調駆動処理部の要部構成を示すブロック図である。

## 【図8】

フリッカーが発生する原因を示す図面である。

## 【図9】

本発明のさらに他の実施形態を示すものであり、変調駆動処理部の要部構成を 示すブロック図である。

## 【図10】

上記変調駆動処理部による変調の程度変更方法を示すものであり、映像データの差と、変調の程度との関係を示すグラフである。

#### 【図11】

他の変調の程度変更方法を示すものであり、映像データの差と、変調の程度との関係を示すグラフである。

#### 【図12】

上記変調駆動処理部の構成例を示すブロック図である。

#### 【図13】

上記変調駆動処理部に設けられたラインメモリの構成例を示すブロック図である。

#### 【図14】

上記変調駆動処理部の動作を示すタイミングチャートである。

#### 【図15】

上記変調駆動処理部の他の構成例を示すブロック図である。

## 【図16】

上記変調駆動処理部の動作を示すタイミングチャートである。

## 【図17】

上記変調駆動処理部の他の構成例を示すものであり、変調駆動処理部の動作を 示すタイミングチャートである。

## 【図18】

往復応答時に応答速度がバラついた状態を示す図面である。

#### 【図19】

従来技術を示すものであり、表示装置の要部構成を示すブロック図である。

## 【図20】

他の従来技術を示すものであり、液晶表示パネルの動作を示すタイミングチャートである。

#### 【図21】

上記両従来技術を組み合わせた場合の動作を示すタイミングチャートである。

## 【図22】

CRTのインタレース表示を示す図面である。

#### 【図23】

液晶表示装置のインタレース表示を示す図面である。

## 【図24】

上記両従来技術を組み合わせた場合に発生する演算対象の不一致を示す図面である。

#### 【符号の説明】

- 1 画像表示装置(表示装置)

- 22~22g 現&前フィールドの映像信号生成部(映像信号生成手段)

- 23~23c 演算回路(駆動信号生成手段)

- 31 ラインメモリ(現フィールドラインメモリ;現フィールド補間手段)

- 41 ラインメモリ (現フィールドラインメモリ;現フィールド補間手段)

- 32・42~42b フィールドメモリ

- 33 · 43 ~ 43 b 調停回路(制御手段)

- 4.4 ラインメモリ(前フィールドラインメモリ;前フィールド補間手段)

- 51・51 c 前々フィールド映像信号生成回路 (同一位置フィールド映像信号生成手段)

- 52 ラインメモリ (前々フィールドラインメモリ)

- 62.62c 比較回路(比較手段)

- 63 変調量調整回路(調整手段)

- 64 ラインメモリ (比較結果ラインメモリ)

- PIX 画素 .

## 【書類名】 図面

# 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図11】

【図12】

## 【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

| N-1行目       | N-1行目                          | N-1行目 N-1行目   | D L (*, j-2, k) D L (*, j-1, k) |

|-------------|--------------------------------|---------------|---------------------------------|

|             |                                |               |                                 |

| N-1行目       | N-1行目                          | N-2行目 N-2行目   | D L (*, j-4, k) D L (*, j-3, k) |

| インタレースの映像信号 | データ信号線<br>駆動回路による<br>データサンプリング | データ信号線駆動回路の出力 | SL1~SLn<br>への出力                 |

【図21】

【図22】

| 偶数フィールド | フィールド1行目 | I        | フィールド2行目 |          | フィールド3行目 |   | • | • | • |

|---------|----------|----------|----------|----------|----------|---|---|---|---|

| 奇数フィールド | フィールド1行目 | フィールド2行目 |          | フィールド3行目 |          | , | • | • |   |

|         | フレーム1行目  | フレーム3行目  | フレーム4行目  | フレーム5行目  | フレーム6行目  |   |   |   |   |

【図23】

| 偶数フィールド | ダミーデータ<br>フィールド1行目<br>フィールド2行目<br>フィールド2行目<br>フィールド3行目<br>フィールド3行目               |

|---------|----------------------------------------------------------------------------------|

| 奇数フィールド | フィールド1行目<br>フィールド2行目<br>フィールド2行目<br>フィールド3行目<br>フィールド3行目<br>フィールド3行目<br>フィールド3行目 |

|         | フレーム1 位置<br>フレーム2 位置<br>フレーム4 位置<br>フレーム5 位置<br>フレーム6 位置                         |

【図24】

| 偶数フィールド   | グミーデータ         フィールド1行目         フィールド2行目         フィールド2行目         フィールド3行目         フィールド3行目         フィールド3行目 |

|-----------|--------------------------------------------------------------------------------------------------------------|

|           | (参照先)                                                                                                        |

| - 本数フィールド | フィールド1行目<br>フィールド2行目<br>フィールド2行目<br>フィールド3行目<br>フィールド3行目<br>フィールド3行目                                         |

|           | フレーム1行目<br>フレーム2行目<br>フレーム3行目<br>フレーム4行目<br>フレーム5行目<br>フレーム6行目                                               |

## 【書類名】 要約書

## 【要約】

【課題】 各フィールド毎に1フレーム分の画素群を駆動することによって輝度を増大し、前フィールドの映像信号を参照して駆動信号を変調することによって画素の応答速度を向上できるにも拘わらず、演算対象のズレに起因する誤変調の発生を防止し、表示品質の良い表示装置を実現する。

【解決手段】 ラインメモリ31は、インタレースの映像信号DATの水平ライン間を補間して、1フレーム分の現フィールド映像信号DAT1を生成する。フィールドメモリ32は、現フィールドの映像信号を次のフィールドまで記憶すると共に、前フィールドの映像信号の水平ライン間を補間して、1フレーム分の前フィールド映像信号DAT0を生成する。さらに、演算回路23は、両映像信号DAT1・DAT0のうち、互いに同じ画素に対応する映像信号同士に基づいて、当該画素へ供給する補正映像信号DAT2を生成する。

## 【選択図】 図1

識別番号

[000005049]

1. 変更年月日

1990年 8月29日

[変更理由]

新規登録

住 所 氏 名 大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社